Xilinx Ten Giga Sub System IP 使用

judy 在 周一, 10/08/2018 - 17:04 提交

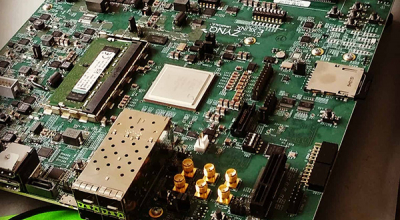

IP核描述

10 Giga Ethernet Sub System , 参考文档PG157:

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

IP核描述

10 Giga Ethernet Sub System , 参考文档PG157:

尽管 Vivado 不支持 “placement cost tale”的功能,InTime 却有一个相似功能叫做“Placement Exploration”配方(Receipe),并且不会对性能产生任何影响。在本文中,我们将通过展示几则用户案例的结果,来了解这个布局配方的作用以及它能对您有哪些帮助。

译 | 王坚 整理 | AI时间

下面是十个Python中很有用的贴士和技巧。其中一些是初学这门语言常常会犯的错误。

注意:假设我们都用的是Python 3

1. 列表推导式

你有一个list:bag = [1, 2, 3, 4, 5]

一、前言

1、介绍

本用户指南介绍了Digilent DVI-to-RGB视频解码器知识产权。 该IP直接连接到Sink器件的DVI 1.0规范中定义的原始转换最小化差分信号(TMDS)时钟和数据通道输入。 它解码视频流并输出24位RGB视频数据以及从TMDS链路恢复的像素时钟和同步信号。

0.顶层Makefile增加交叉编译器

顶层makefile:

ARCH ?= $(SUBARCH)

CROSS_COMPILE ?= $(CONFIG_CROSS_COMPILE:"%"=%)

Vivado Simulator基本操作

Vivado Simulator是一款硬件描述语言事件驱动的仿真器,支持功能仿真和时序仿真,支持VHDL、Verilog、SystemVerilog和混合语言仿真。点击运行仿真后,工具栏中显示了控制仿真过程的常用功能按钮:

什么是ttl电平

TTL电平信号被利用的最多是因为通常数据表示采用二进制规定,+5V等价于逻辑"1",0V等价于逻辑"0",这被称做TTL(晶体管-晶体管逻辑电平)信号系统,这是计算机处理器控制的设备内部各部分之间通信的标准技术。

一、AXI DMA介绍

【导读】Python在解决数据科学任务和挑战方面处于领先地位。而一些方便易用的库则帮助了开发人员高效开发。在这里我们整理了20个在深度学习、数据分析中最常用、最好用的Python库,供大家一起学习。

作者| ActiveWizards

编译|专知

整理|Yingying,李大囧

核心库与统计