MPSOC之1——overview、开发板、工具

judy 在 周五, 09/14/2018 - 10:34 提交

1.MPSOC overview

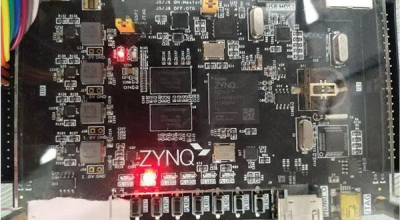

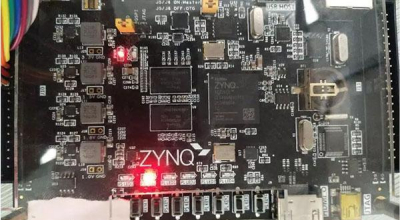

MPSOC是xilinx公司推出的新一代集成SOC,比ZYNQ厉害了一个等级。

熟悉一个芯片,不能一头扎进详细的数据手册,应该从overview开始大概了解,然后浏览user manual的前几章,具体外设用时细读。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

1.MPSOC overview

MPSOC是xilinx公司推出的新一代集成SOC,比ZYNQ厉害了一个等级。

熟悉一个芯片,不能一头扎进详细的数据手册,应该从overview开始大概了解,然后浏览user manual的前几章,具体外设用时细读。

从Vivado开始,配置GTX的时候,多了一个SATA协议支持,但有些小地方还需要自己另外设置。整理了一下,分享给大家。

首先打开Transceivers wizard:

SSN概述

作者:OpenSLee

1 背景知识

Zynq的IO包括对外连接的GPIO和内部PS与PL通信的AXIO。其中对外的GPIO又分为两种:MIO和EMIO。MIO直连到PS;EMIO则是PS扩展到PL,从PL接出的IO。所以MIO不需要管脚约束,而EMIO需要管脚约束。

1.MIO寄存器

本文是该系列的第17篇。上一篇介绍了使用低层次封装的block搭建直接型FIR滤波器结构的方法,对设计进行时序分析,并将设计流水线化来提高系统的工作频率。转置型FIR滤波器是一种由直接型FIR滤波器变换而来的结构,在几乎相同的结构下有着更好的性能,本文将对此做介绍。

转置型FIR滤波器

滤波器结构框图如下:

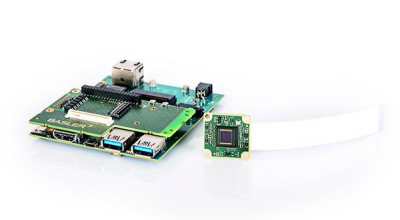

近年来,市面上已涌现出越来越多的嵌入式视觉应用,它们是由嵌入式计算板和相机模块组成的系统。与其他系统相比,这类系统能以更经济、更有效的方式管理视觉任务。

相机接口在上述嵌入式视觉系统的设置中扮演着关键作用,因为它承担着将相机模块与主机连接在一起的重任。

作者:OpenSLee

1 背景知识

电子相册的实现就是通过按键来改变显示器的图片轮换。本节将通过ps端的按键来控制ARM选择不同的图片通过HDMI输出到显示屏。

1.1 AXI_VDMA的介绍

引言

什么叫做“嵌入式视觉”?

嵌入式视觉=小型处理板 + 小型相机模块

在嵌入式视觉领域中,处理器有许多分类,SoC, SoM,SBC,FCD分别是什么?他们之间有什么区别和联系?通过本文,您可以有个系统的归纳和了解。

片上系统(SoC)

在I/O和时钟规划之后,需要验证设计以确保其满足设计需求。Vivado提供了两种验证途径:DRCs用来检查设计违反规则情况;SSN分析用来估计转换噪声等级。本文将介绍DRCs,本系列第16篇介绍了SSN分析。