AMD芯片在3D重建中的应用分析

judy 在 周五, 05/09/2025 - 14:52 提交

3D重建通过精确捕捉物体表面几何信息,构建出高精度数字模型,在多个行业中获得了广泛应用。从工业制造、航空航天,到文物保护、建筑工程等领域

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

3D重建通过精确捕捉物体表面几何信息,构建出高精度数字模型,在多个行业中获得了广泛应用。从工业制造、航空航天,到文物保护、建筑工程等领域

本文将探讨优化数据传输、AI 引擎加速以及动态功能交换(DFX)的关键技术,以全面释放 AMD Versal SoC 的潜能。

eSPI总线具有低功耗、管脚数量少、高效的数据传输等优点,常用于与EC、BMC、SIO等外设的通信,是PC中CPU与这些外设通信的主流协议

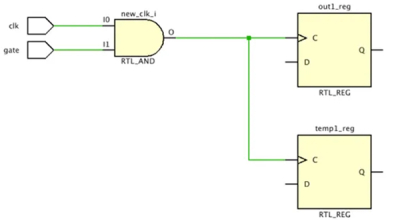

传统上,使用门控时钟是 ASIC 设计中降低系统功耗的常见方法。通过门控时钟,可在非必要时阻止整组寄存器的状态转换。

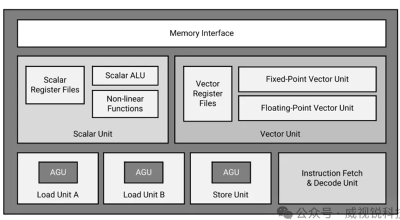

AI Engine是一款高度优化的处理器,具有单指令多数据(SIMD)和超长指令字(VLIW)处理器,支持定点和浮点精度。

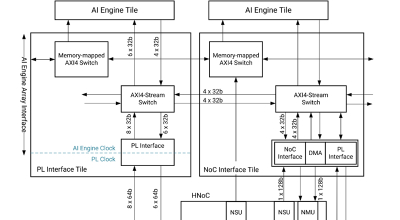

AI Engine阵列界面有三种类型的AI Engine界面平铺。AI Engine阵列的每一列都有一对一的接口Tile对应

这篇博客旨在逐步演示如何使用 Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器

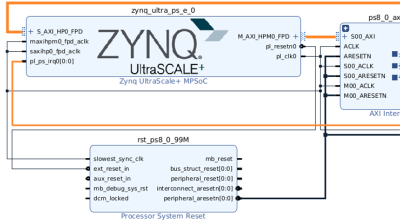

这是一块基于 AMD Versal Edge AI 平台的开发板,功能特别强大,可以用来做图像处理、人工智能等各种高阶应用。

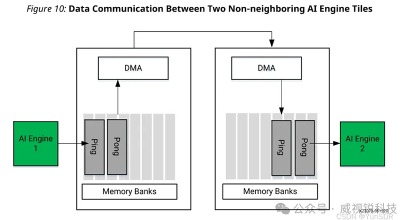

本节描述了AI Engine阵列内以及AI Engine Tile和可编程逻辑(PL)之间的数据通信示例。

本文讲述了如何使用 One Spin 检查 AMD Vivado™ Design Suite Synth 的结果(以 Vivado 2024.2 为例)。