从FPGA说起的深度学习(六)-任务并行性

judy 在 周三, 04/12/2023 - 09:32 提交

在本教程中,旨在加深对深度学习和 FPGA 的理解

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

在本教程中,旨在加深对深度学习和 FPGA 的理解

最近有客户反馈,U-Boot 2020.2 启动有问题

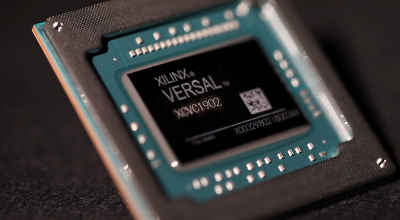

Versal SYSMON 是通过 Vivado 中的 CIPS GUI 来配置的。您可以通过寄存器存取来对 SYSMON 进行寻址

本文演示了在Vitis™ 中对 Linux 应用程序开发的过程中如何使用外部库

本文将演示如何在 IP integrator 内使用 CIPS Wizard 设置“System Monitor”(系统监控器)

EtherCAT现场总线协议是由德国倍福公司在2003年提出的,该通讯协议拓扑结构十分灵活,数据传输速度快

在Versal Advanced IO Wizard中,所包含的PLL的去歪斜电路可能导致数据速率较高时出现建立时间

深度学习处理器 (DPU) 是一个专为深度神经网络而优化的可编程引擎。它由一组可参数化的 IP 核组成

串行通信技术(Serial Communication),是指通信双方按位bit进行,遵守时序的一种通信方式

VCK5000在vitis ai 3.0对应的shell版本为xilinx-vck5000-gen4x8-qdma-base_2