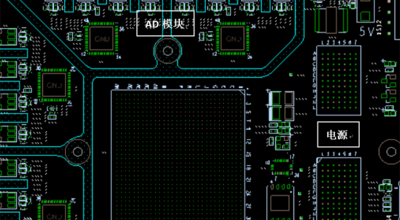

串行ADC布局布线设计要点!

judy 在 周一, 05/15/2023 - 09:30 提交

本文给大家分享串行ADC布局布线设计要点!

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

本文给大家分享串行ADC布局布线设计要点!

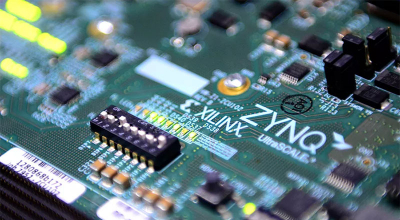

探讨如何在 Zynq UltraScale ZCU104 开发板上通过 PSU DDR 执行 MicroBlaze 应用

有客户需要通过PCie从Windows系统访问MPSoC的DDR,从而使X86和A53通过共享DDR内存的方式交互大量数据

AMD FPGA支持的MultiBoot特性,可以使FPGA先尝试启动最新的配置(bit)文件

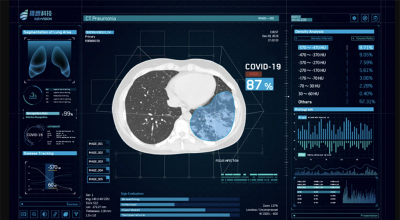

新冠疫情已基本宣告结束,但其给医疗系统带来的巨大冲击,仍值得我们深思

近些年来,随着自动控制领域的发展,摄像镜头的工艺和视觉识别算法越来越完善

Zynq UltraScale+ PS MIO 可能在 VCCO_PSMIO 电源上电缓升期间输出高位毛刺

本文详细介绍基于北京芯加速科技的VU13P平台,使用AXI Chip2Chip IP,开发测试了一套用于ASIC验证仿真的片间通信方案。

在 CIPS GUI 中已对 Versal System Monitor 过热 (OT) 告警进行了说明