【XDF资料下载】收敛 IO 加速平台

judy 在 周四, 01/03/2019 - 11:49 提交

本演讲资料介绍了:

本演讲资料介绍了:

FPGA设计中经常用到一些控制逻辑,如有限状态机(FSM),如果用各种block搭建一个FSM比较麻烦。System Generator支持调用MATLAB代码,通常可以编写MATLAB代码来实现FSM等控制逻辑,通过MCode block调用到System Generator设计中。

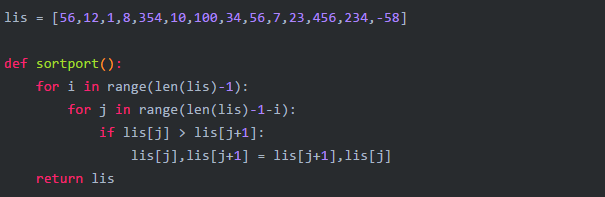

1、冒泡排序

2、计算x的n次方的方法

在本次研讨会中,赛灵思专家将向您介绍赛灵思MicroBlaze 处理器将如何让启动新设计变得前所未有地简单快捷!无需 RTL 经验就能使用 Vivado IP 集成器工具以及第三方 IP 库。专家将为您演示如何使用外围设备在几分钟之内快速打造任何嵌入式设计原型

2018年,从FPGA到加速器卡到新型的器件类别的各种技术创新上, 赛灵思都取得了重大进展。我们期待着借助这些前沿的技术,支持所有的开发者, 加速所有的创新应用, 携手客户和合作伙伴创造新的辉煌

本指南介绍 了动力总成HIL测试的最佳工程实践 本应用指南介绍了动力总成HIL测试的最佳工程实践。 通过本指南,了解高效构建HIL测试仪所需的工具和视角,以确保最大化测试覆盖率以及系统能够满足未来的技术要求。

本文主要介绍Zynq UltraScale + MPSoC系列芯片的USB3.0/2.0接口硬件设计。

1. 首先要在Ubuntu下安装Petalinux 2017.2

2. 设置Petalinux 环境变量

source /

3. 新建目录~/projets/fpga-drive-aximm-pcie

4. 把Windows下的Vivado工程复制到~/projets/fpga-drive-aximm-pcie下

5. 新建Petalinux工程

petalinux-create --type project --template zynq --name petalinux_prj

6. 切换到petalinux_prj目录

cd petalinux_prj/

7. 导入HDF

petalinux-config --get-hw-description ../fpga-drive-aximm-pcie-2017v2_hpc/Vivado/zc706_hpc_pcie/zc706_hpc_pcie.sdk/

随之弹出Linux System Configuration界面,不做任何更改,保存退出

据麦姆斯咨询介绍,目前,对于科技公司和汽车厂商的高管和工程师来说,自动驾驶汽车(AV)技术及其发展路线图上还有很多问题有待解决。其中,三个悬而未决的大问题正在突显。

无线工程师经常希望使用无线信号实现从概念到原型。诸如USRP(通用软件无线电外设)设备的软件无线电(SDR)提供了满足该需求的灵活解决方案