AMD将投资1.35亿美元 扩大爱尔兰自行调适运算研发与工程营运

judy 在 周五, 07/07/2023 - 10:00 提交

AMD宣布,将在4年内投资高达1.35亿美元,持续推动爱尔兰的业务成长

AMD宣布,将在4年内投资高达1.35亿美元,持续推动爱尔兰的业务成长

在这个项目中,将在线和离线 TSM 网络部署到 FPGA,通过 2D CNN 执行视频理解任务

AMD最新的Epyc处理器将服务器阵容扩展到128核,使用更小、更节能的Zen 4C CPU

本文介绍协议之间的一些关键差异和对每种协议进行简要说明

当前,我国已经建成全球技术最先进、规模最大的5G独立组网

此次研讨会将覆盖AMD在工业自动化和汽车电子领域的最新应用

该新系列非常适合需要低功耗和高 I/O 的成本敏感型应用,其面向广泛的行业

Vitis高层次综合可通过在选定的 AMD 器件上将 C/C++ 代码综合为可编程逻辑的 RTL 代码

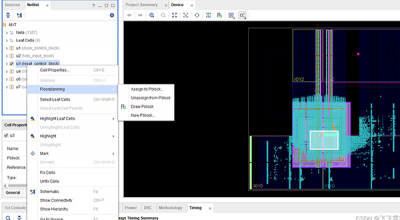

时钟是每个 FPGA 设计的核心。如果我们正确地设计时钟架构

作为一名刚入坑的新手小白,我将分享自己的一些建议