罗德与施瓦茨、藤仓、艾福伦验证了用于5G毫米波相控阵天线研发测试的CATR OTA测试系统

judy 在 周日, 06/25/2023 - 15:52 提交

系统架构师可以使用该套件来为5G毫米波系统使用Zynq® UltraScale+™ RFSoC Gen3

系统架构师可以使用该套件来为5G毫米波系统使用Zynq® UltraScale+™ RFSoC Gen3

使用 Vivado 或 Vitis_Analyser 时,工具发生崩溃并显示一下错误

该项目展示了一些红外图像处理算法,这些算法可以提高图像质量

随着 5G 将网络推向更高频率,无线基础设施需要全面的小型蜂窝密集化

爱瑞无线基于AMD RFSoC FPGA芯片推出5G加速卡AVDU1010

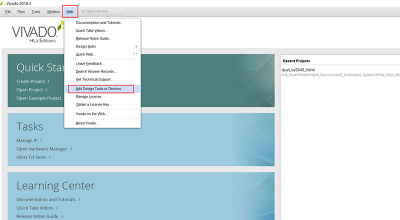

打开vivado,选择help,点击Add Design Tools or Devices

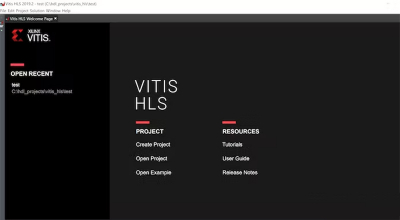

Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS

本文介绍VVAS框架所支持调用的H/W(HLS)内核

你想了解Vitis L1库吗?Vitis HLS 2023.1支持一个新的L1库向导