使用VVAS开发软件应用

judy 在 周一, 06/19/2023 - 14:40 提交

Vitis视频分析SDK是在AMD平台上构建AI驱动的智能视频分析解决方案的完整软件栈

Vitis视频分析SDK是在AMD平台上构建AI驱动的智能视频分析解决方案的完整软件栈

在前面的文章中主要介绍了hash表及其链表的结构,同时说明了如何读取表项

VADJ 引脚是 VITA 57.1 FMC 标准的一部分,承载着从载卡到 I/O 夹层模块的可调节电压等级的电源

Lisa Su 深入探讨如何使用该公司多年来一直使用的小芯片来构建这些芯片

本答复记录旨在描述在部分 Versal 自适应 SoC 器件上使用物理不可克隆功能

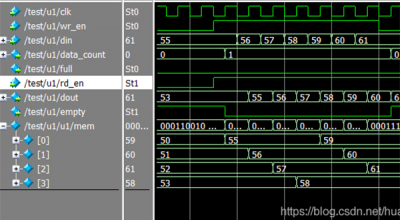

为了应付找工作的需要,打算学习一些fifo相关的内容,首先是从fifo的设计开始

AMD 推动数据中心专业计算性能,推出适用于云原生和技术计算的全新 AMD EPYC处理器

亚马逊EC2 M7a实例提供了性能上的重大飞跃,其计算性能比M6a实例高出50%