DMA/Bridge Subsystem for PCI Express 产品指南 (v4.1)

judy 在 周三, 03/22/2023 - 09:34 提交

赛灵思 DMA Subsystem for PCI Express® 可实现高性能、可配置的分散聚集 DMA

Vitis软件平台由适用于交互式工程开发的集成设计环境和适用于脚本化或手动应用开发的命令行工具组成

本文将讲述如何使用Verilog 编写一个基础的测试脚本(testbench)。

在vivado-Tool-setting-project-setting-synthesis路径下,设置 -mode out_of_context

Vitis HLS 2022.1新增了一个pragma名为performance,其施加对象是指定函数或循环

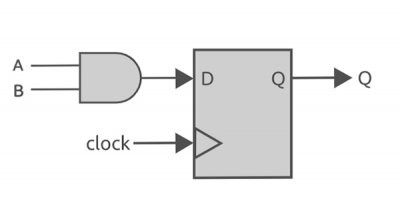

本文整理了数字电路课程中的相关基本的知识点和较为重要的知识点,用于求职的数电部分的知识准备

时序约束主要包括周期约束,偏移约束,静态时序路径约束三种

在不带内置ARM核的AMD FPGA产品系列中,FPGA的程序加载方式并没有发生大的变化