RFSoC应用笔记 - RF数据转换器(8):RFSoC关键配置之RF-DAC内部解析(二)

judy 在 周四, 12/29/2022 - 11:14 提交

本文主要对RF-DAC 奈奎斯特区操作、逆sinc滤波器以及数据通路的相关操作进行介绍。

本文主要对RF-DAC 奈奎斯特区操作、逆sinc滤波器以及数据通路的相关操作进行介绍。

路径1、2、3实际上都是对寄存器到寄存器之间的数据路径之间的约束,而路径4则是约束纯组合逻辑

在本文中,我们回顾了该公司的过去,审视了通往现在的道路上的曲折,并想知道这家硅谷资深企业的未来。

经常有人问,为什么嵌入式系统的底层软件,出问题后解决起来,耗时长

VeriTiger®-OV19P单系统提供 8颗灵活配置的Xilinx XCVU19P FPGA,提供100多种配套子卡资源

今天给大家普及一下阻塞赋值和非阻塞赋值的相关知识

时钟线能持续不断将逻辑级别脉冲至高位和低位,每次脉冲之间持续时间“tb”以脉冲宽度来表示

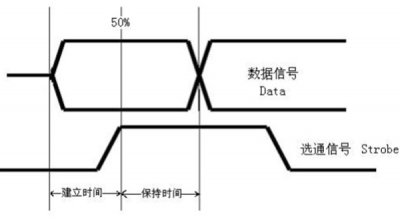

针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源同步时序系统

本节开始我们介绍7系列FPGA收发器接收部分结构

本文参考官方手册,主要对RF-DAC 模拟输出进行介绍。