Xilinx FPGA资源解析与使用系列——Transceiver(十一)transceiver与用户数据的接口

judy 在 周二, 11/29/2022 - 09:02 提交

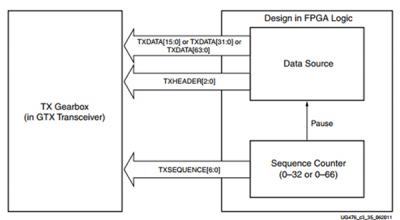

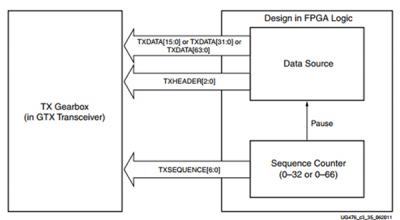

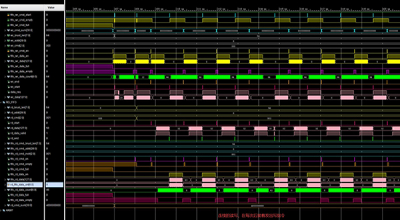

本文主要讲transceiver与用户逻辑数据的接口

本文主要讲transceiver与用户逻辑数据的接口

Vitis-AI在边缘计算设备的AI全栈部署框架中扮演了编译器端与后端的角色,接收前端 DNN 框架训练后的网络参数IR

在之前设计的 DDR3 控制器的基础上,添加用户写、读模块,便于在用户端更容易的对 DDR3 进行写读控制

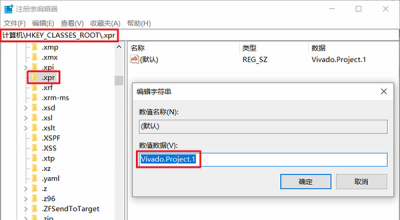

之前安装的Vivado 2018.3,最近装了Vivado 2020.2,然后就没法双击打开xpr工程文件了

基于AMD有史以来性能最强的“Zen 4”核心,该处理器可提供业界领先的性能和能效

本指南涵盖了以下设计流程:硬件、IP和平台开发。

我们主要关注的是TXDIFFCTRL 摆幅、Pre-Emphasis 预加重、Post-Emphasis 去加重

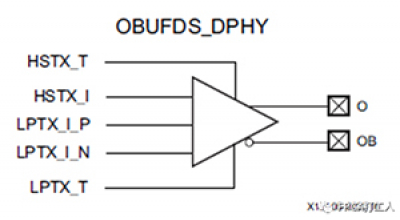

新的DSI-2协议定义了两个高速串行数据传输接口选项

在读写模块的基础上添加 FIFO 接口,包括写指令 FIFO、写数据 FIFO

宜鼎FPGA平台采用AMD Xilinx Kria K26系统模块,不仅能够加速AI演算,同时具备低延迟、低功耗特性