【工程师分享】eglfs_kms的QT程序,如何同时支持两个显示器

judy 在 周一, 09/27/2021 - 12:13 提交

有客户问到如何在ZCU106单板/其它MPSOC上,同时支持多个显示器,以便在多个显示器上运行QT应用程序。Xorg的xorg.conf里可以增加card和screen,同时支持多个显示器。Xorg可以在多个显示器上显示多个QT应用程序。

有客户问到如何在ZCU106单板/其它MPSOC上,同时支持多个显示器,以便在多个显示器上运行QT应用程序。Xorg的xorg.conf里可以增加card和screen,同时支持多个显示器。Xorg可以在多个显示器上显示多个QT应用程序。

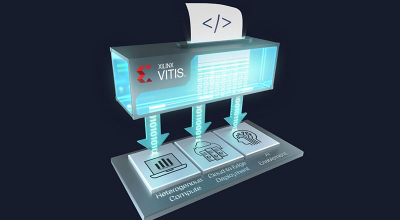

本文对vivado、vitis、petalinux2021.1版本以及Vitis AI 1.4安装过程进行详细描述,并提供安装软件网盘地址。

通用串行总线(Universal Serial Bus)是连接计算机系统与外部设备的一种串行总线标准,也是一种输入输出接口的技术规范,被广泛地应用于个人电脑和移动设备等信息通信产品。USB总线是最复杂的总线之一,但其广泛使用。本文首先直接使用USB相关的驱动的应用,后面再具体开始编程做自己的USB驱动程序。

本篇博文中的分析是根据真实客户问题撰写的,该客户的 DFX 设计无法连贯布线,存在布线重叠。本篇博文旨在演示用于缩小根本原因范围以及修复此问题的部分调试技巧。

通过如下流程,可以给视频码流添加PTS和用户自定义信息

|

|

课程主题:GPU及相关技术概览(含Demo实操)

在百度edgeboard fzu3上运行CIFAR10 Classification,介绍Vitis AI TensorFlow设计过程,将Python描述的网络模型运行在Xilinx DPU上。

本文简要介绍CAN总线协议,以Linux驱动CAN网络为重点介绍。

赛灵思今日宣布,双方正合作开发 NEC 的下一代 5G 无线电单元( RU),预计 2022 年可用于全球部署。赛灵思 7nm Versal AI Core 系列器件现已量产出货,将助力全新 NEC RU 实现更出色的性能。这些最新型 NEC 5G 大规模 MIMO RU 利用数字波束成形带来更高效的通信和更高带宽。NEC RU 旨在满足全球市场需求,将支持C-Band 在内的多种 5G 频段。

视频分析在我们生活中的许多方面都越来越多地被使用,无论是在智能楼宇中通过人脸识别控制安全点,从而提供比门禁卡更加可靠的安全性,还是监测是否符合佩戴口罩和保持社交距离,从而满足新冠疫情的抗疫要求,也或是监测交通拥堵和发现犯罪的智慧城市部署,视频分析应用无处不在