挑战赛全知道: 参考资料大全!

judy 在 周五, 09/24/2021 - 09:57 提交

近日,赛灵思携手 Hackster.io 再次向开发者发起了自适应计算的挑战。比赛开启短短2周,我们收到了全球开发者的踊跃报名以及硬件申请,为了更好地服务中国区的开发者参加比赛,XILIINX开发者社区整理了三大赛道可用到的参考资源,祝大家一臂之力!

近日,赛灵思携手 Hackster.io 再次向开发者发起了自适应计算的挑战。比赛开启短短2周,我们收到了全球开发者的踊跃报名以及硬件申请,为了更好地服务中国区的开发者参加比赛,XILIINX开发者社区整理了三大赛道可用到的参考资源,祝大家一臂之力!

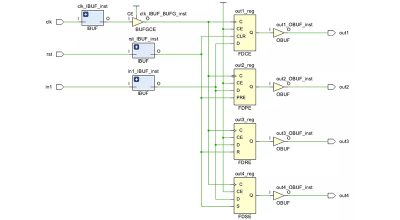

今天我们来研究一下D触发器都有哪几种类型?又对应什么样的代码?

医疗服务提供商收集的数据量正在不断增长,并正在颠覆当前的数据分析方法。与此同时,跨表格和业务实体联网并识别隐含关系与模式的能力,为提升患者护理和患者疗效以及为医疗服务提供商降本增效方面,提供了诱人的突破。

过去 20 年里,金融交易技术领域风起云涌:电子交易、算法、智能订单路由器持续演进;高频交易( HFT )兴起;为追求增强收益而寻找更复杂的阿尔法 ( Alpha )搜索策略。伴随这些趋势,金融交易指令也经历了重大变化。

如何将Vitis AI Library应用加入Vitis进行编译,生成可执行文件?

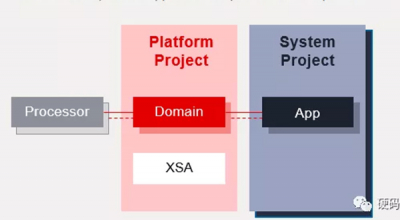

Kria™ 机器人堆栈 (KRS) 是一组集成的机器人库和实用程序,它们使用硬件来加速工业级机器人解决方案的开发、维护和商业化。它采用 ROS 2 作为软件开发工具包 (SDK),并提出了一种以 ROS 2 为中心的开发方法,涵盖从计算图的创建到 Xilinx App Store 中的 ROS 2 覆盖工作区的商业化。

在过去,当软件工程师在CPU或者GPU上面进行开发时,需要改变或优化软件来适应硬件。但是随着近些年的人工智能,机器学习等科技的发展及普及,所有的软件开发者都在寻找一种让硬件适用软件的方式,由此提升程序开发的效率。同时也需要一个平台来适应各类开发人员的使用需求,这时候新的计算方式就应运而生了。

Zynq&ZU+ Mpsoc的以太网使用普遍,从功能大致分为2类应用:调试管理、数据传输。本文主要集中在PS端的Ethernet RGMII外接phy设计和调试,该部分客户用的最多也最容易出问题,希望通过本文对基于RGMII+phy的典型应用快速入门,解决问题。

近日,OpenPOWER 基金会执行董事 James Kulina 在印度知名高等学府印度理工学院鲁尔基分校(IIT Roorkee)与 OpenPOWER 及 IBM 联合举办的OpenPOWER 堆栈技术研讨会上,分享了OpenPOWER基金会的最新进展及未来发展方向。

在Vivado工程的调试中,xdc文件指定管脚后,我们偶尔会临时修改管脚位置,但之前的位置信息还想保留在xdc中,因此很多工程师就会选择将之前的管脚信息注释在修改位置的后面。比如下面的工程中,rxd_pin的位置本来是F25,我们需要临时改成E17,同时把F25注释到后面,表明这个位置之前是F25