【下载】Versal ACAP SelectIO资源架构手册

judy 在 周二, 03/30/2021 - 09:48 提交

本文描述Versal™设备中可用的SelectIO™资源。

本文描述Versal™设备中可用的SelectIO™资源。

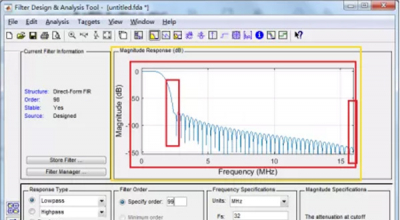

本讲在Vivado调用FIR滤波器的IP核,使用上一讲中的matlab滤波器参数设计FIR滤波器,下两讲使用两个DDS产生待滤波的信号和matlab产生带滤波信号,结合FIR滤波器搭建一个信号产生及滤波的系统,并编写testbench进行仿真分析

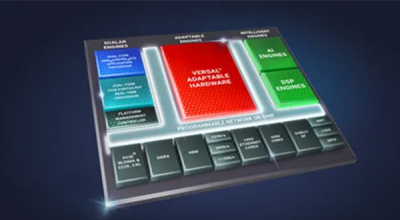

本视频简要介绍了 Vitis AI Edge IP 的计划和架构,包括全新 1.3 版本中的新增功能。

4月22日-23日,赛灵思举办 Adapt China:Vivado专场,特邀Vivado专家团队,与您分享 Vivado 在设计自动化集成、IP子系统复用和加速设计收敛等方面的方法和技巧。

本文以99阶FIR低通滤波器为例,学习使用matlab的fdatool工具箱设计滤波器,并将滤波器系数导出到.coe文件,联合Vivado进行FPGA的FIR滤波器设计

中文版 Parallel Programming for FPGAs(pp4fpgas, FPGA并行编程-以数字信号处理为例)是本公众号最受欢迎的内容之一,中文书稿和开源项目截止目前已有数万的访问量。这本书也是许多不熟悉FPGA的开发者在从PYNQ入门后,进行算法硬件实现的第一本入门宝典

赛灵思Vitis AI开发环境的正确安装姿势

Xilinx自适应器件的灵活性和可配置性与IP和工具产品相结合,可显著提高安全处理性能。

本视频快速介绍 Vitis AI Model Zoo 的计划和内容,包括全新 1.3 版本中的新增功能。

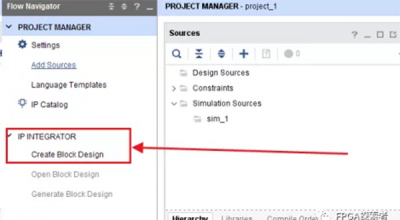

因为 BD 中连线太多,所以想自定义下 interface 简化连线,定义好了一个 interface,但当准备在自定义 IP 中指定它时,发现我把一个信号的方向搞错了,应该定义成 out,但实际定义成了 in,所以想简单的改一下方向。