赛灵思 App Store, 助力万物加速!

judy 在 周五, 03/19/2021 - 10:31 提交

赛灵思应用商店 (Xilinx App Store) 是赛灵思首次面向广大用户所提供的数字化自适应加速应用发布平台,其加速应用来自赛灵思、第三方合作伙伴和优质独立软件开发商。目前,Xilinx 应用商店支持多种领域的加速计算,包括视频及图像处理、数据分析、高性能计算、机器学习及网络安全等

赛灵思应用商店 (Xilinx App Store) 是赛灵思首次面向广大用户所提供的数字化自适应加速应用发布平台,其加速应用来自赛灵思、第三方合作伙伴和优质独立软件开发商。目前,Xilinx 应用商店支持多种领域的加速计算,包括视频及图像处理、数据分析、高性能计算、机器学习及网络安全等

您所不知道的 Xilinx:深耕汽车市场 20 年的故事

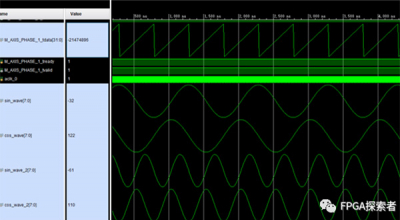

本次使用Vivado调用DDS的IP进行仿真,并尝试多种配置方式的区别,设计单通道信号发生器(固定频率)、Verilog查表法实现DDS、AM调制解调、DSB调制解调、可编程控制的信号发生器(调频调相)。

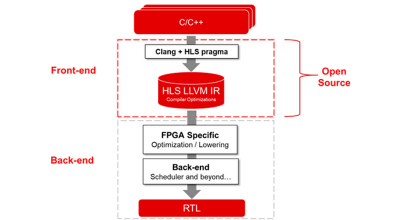

赛灵思一直致力于支持开源计划的不断飞跃,为帮助开发人员和研发社区充分发挥自适应计算的优势,我们再次做出了令人振奋的举措: 在 GitHub 上开放提供 Vitis HLS(高层次综合)前端。Vitis HLS 工具能够将 C++ 和 OpenCL™ 功能部署到器件的逻辑结构和 RAM/DSP 块上。

随着技术的发展与革新,服务器、SmartNIC与DPU之间的界限越来越模糊,但实际上,定义与用例之间几乎没有多大关系。今天,我们针对Xilinx日前推出的新一代Alveo SmartNIC产品组合,从中窥探SmartNIC的未来发展趋势:可组合性。

了解全新的 16nm Artix® UltraScale+™ FPGA 系列和 Zynq® UltraScale+ MPSoC ZU1 器件,以超紧凑的封装提供,可为成本敏感型的边缘和网络应用提供无与伦比的计算密度。

本文档旨在描述推荐的设计方法,帮助用户在 Vivado® Design Suite 中有效利用赛灵思 FPGA 器件资源,并加速完成设计实现和时序收敛。提供推荐方法背后的原理,以支持用户制定出明智的设计决策。

一图读懂赛灵思全新UltraScale+成本优化型产品组合

赛灵思今日宣布面向市场扩展其 UltraScale+ 产品组合,以支持需要超紧凑及智能边缘解决方案的新型应用。新款 Artix® 和 Zynq® UltraScale+ 器件的外形尺寸较传统芯片封装缩小了70%,能够满足工业、视觉、医疗、广播、消费、汽车和互联市场等更广泛的应用领域。

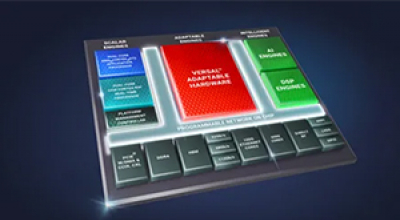

身处智能时代,科技发展日新月异,伴随数据中心、有线网络、5G 无线和汽车等愈加丰富的场景,相应的技术与功能也正经历飞速迭代,因此,单一计算架构已难以应对海量数据处理需求,赛灵思 Versal ACAP多核异构计算平台致力于帮助所有开发者保持即时的灵活应变能力。