一种基于VPX架构的高速宽带通信平台设计

judy 在 周五, 04/02/2021 - 10:06 提交

本文介绍了一种基于VPX架构的高速宽带数据通信平台,平台的核心是机载和地面收发信机,收发信机内各功能板卡的主要控制器是FPGA。发射端对信息序列进行打包、信道编码、交织和调制;接收端对信号进行解调、解交织、解码、同步等操作。还原后的信息上传至上位机进行分析。

本文介绍了一种基于VPX架构的高速宽带数据通信平台,平台的核心是机载和地面收发信机,收发信机内各功能板卡的主要控制器是FPGA。发射端对信息序列进行打包、信道编码、交织和调制;接收端对信号进行解调、解交织、解码、同步等操作。还原后的信息上传至上位机进行分析。

本文描述了使用 Vivado工具为 7 系列 FPGA 生成和编程加密位流和加密密钥的过程。

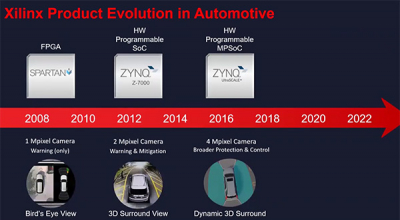

本视频将介绍赛灵思在ADAS和自动驾驶应用领域提供的独特技术优势。

以太网 IP 核的 1588 功能是用来实现,在 IP 内部为TX侧发送包打上发送出去这个时间节点的时间戳,以及获得 RX 侧收回来的包在 IP 接口处的时间戳。然而10G/25G 的 IP 例子工程没有提供演示,本文主要介绍了如何使用这个 IP 的 1588功能。

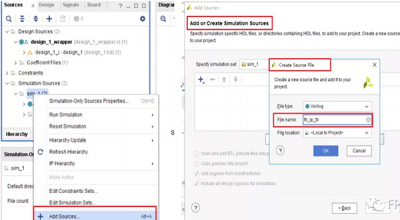

本讲使用两个 DDS 产生待滤波的信号和matlab产生带滤波信号,结合 FIR 滤波器搭建一个信号产生及滤波的系统,并编写 testbench 进行仿真分析,第五讲、第六讲开始编写 verilog 代码设计FIR滤波器,不再调用IP核。

我们在进行HLS编译的时候会设置顶层文件,顶层文件中包括形参、返回值等等。这些映射到硬件电路中会产生信号,这些信号具体又遵循什么样的接口描述我们需要设置,这不仅可以帮助我们设置更优的约束条件使得编译出来的硬件电路更加完美,更重要的是可以让我们精确了解端口所遵循的时序

本应用笔记提供了防篡改(AT)指南和实际案例,以帮助保护UltraScale™和UltraScale+™ FPGA启用的系统中可能存在的IP和敏感数据。

本次活动为 软件与AI专场,通过一系列详细的技术分享与案例解析,与观众面对面探讨更多 FPGA/SOC 领域的创新可能,助力 AI 与软件相关从业者迅速学习掌握赛灵思全新的 Vitis/Vitis AI 统一软件平台。活动也同步聚焦行业热点应用,并介绍针对性的解决方案。

本视频将重点介绍高级驾驶辅助系统中的汽车架构和自动驾驶。

本讲使用matlab产生待滤波信号,并编写testbench进行仿真分析,在Vivado中调用FIR滤波器的IP核进行滤波测试,下一讲使用两个DDS产生待滤波的信号,第五讲或第六讲开始编写verilog代码设计FIR滤波器,不再调用IP核。