【Vitis指南】:Xilinx Vitis 系列(一)

judy 在 周五, 04/09/2021 - 09:43 提交

今天带来第一篇,介绍Vitis 2019.2软件平台发行说明、安装以及Vitis加速环境简介。

今天带来第一篇,介绍Vitis 2019.2软件平台发行说明、安装以及Vitis加速环境简介。

作为全球唯一基于16纳米技术的成本优化型产品组合,UltraScale+ 器件采用台积电最先进的InFO(Integrated Fan Out,集成扇出)封装技术。借助InFO技术,UltraScale+ 器件能以紧凑的封装提供高计算密度、出色的性能功耗比以及可扩展性,从而应对智能边缘应用的需求。

时序约束中的 set_input_delay/set_output_delay 约束一直是一个难点,无论是概念、约束值的计算,还是最终的路径分析,每一次都要费一番脑子。Vivado为方便用户创建输入输出接口的约束,整理出了一套非常实用的InputDelay/Output Delay Constraints Language Templates。

本文详细介绍Vivado工具中Tcl脚本的使用,查询和修改自定义流程的内存设计。讨论如何使用Tcl过程来定义和共享自定义命令。提供了遍历设计层次结构、访问设计对象和处理自定义报告的步骤。

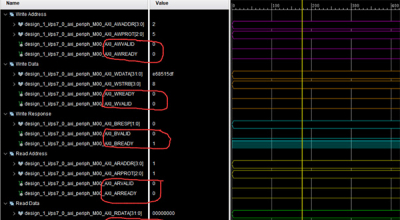

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整个 AXI4-Lite 源码进行分析。

Phantom Intelligence 的 Flash LiDAR 通过其解决范围、可靠性和成本挑战的解决方案,解决了其他传感器无法解决的挑战。包含可编程逻辑和 Arm® 处理器的 Xilinx® Zynq®-7000 SoC 有助于在 Phantom Intelligence LiDAR 中支持复杂的处理,这是系统范围内边缘处理的关键要素

在赛灵思推出的 Zynq UltraScale+ MPSoC白皮书中,详细解读了基于 InFO 封装的全新 Zynq UltraScale+ MPSoC 如何实现紧凑型工业摄像头,并全面展现了其所具备的优秀的性能、功耗比等优势。

百度大脑EdgeBoard AI计算盒/计算卡系百度与米尔联合推出的一款高性能,高可靠性的AI计算盒/计算卡。该产品基于Xilinx Zynq UltraScale+ MPSoC 系列 FPGA可伸缩计算架构,可支持二次开发,支持高精度模型/多模型部署

作为自适应计算的领导者,赛灵思技术日活动将于4月22日来到深圳。届时,赛灵思技术专家将到场分享 FPGA/SoC 领域的创新可能。同时,丰富的干货课程有助于 AI 与软件领域从业者迅速掌握赛灵思全新的 Vitis/Vitis AI 统一软件平台。