【Vivado Design Suite 用户指南】:设计分析与收敛技巧

judy 在 周日, 04/25/2021 - 10:20 提交

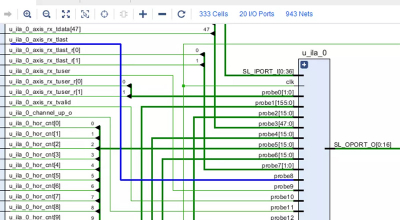

本文详细介绍Vivado工具对FPGA设计进行逻辑和时序分析的特点,以及工具生成的报告和信息。讨论实现时序收敛的方法,包括审查时钟树和时序约束,设计底层规划,以及平衡运行时间和结果。

本文详细介绍Vivado工具对FPGA设计进行逻辑和时序分析的特点,以及工具生成的报告和信息。讨论实现时序收敛的方法,包括审查时钟树和时序约束,设计底层规划,以及平衡运行时间和结果。

在工业现场的设备运维管理,从第一代人工观测,到第二代的定期仪器检测,再到第三代的实时状态检测,直至现在过度到了利用云计算,大数据,人工智能技术主动的预测设备运营状态,根据各传感器信息和设备运行数据提前预测设备的更新和维护。

本视频由 Xilinx 合作伙伴和加速应用程序提供商 Pinnacle Imaging Systems 推出,描述了 Denali 3.0 HDR 图像信号处理器(ISP)的功能。

在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。

详细了解 Kria KV260 Vision AI 入门套件和随附的基本配件包。我们将向您展示在没有 FPGA 经验的情况下,如何快速、轻松地启动并运行我们的智能相机加速应用。

Xilinx FPGA都有一个独特的 ID ,也就是 Device DNA ,这个 ID 相当于我们的身份证,在 FPGA 芯片生产的时候就已经固定在芯片的 eFuse 寄存器中,具有不可修改的属性。在xilinx 7series 和 7series 以前,ID 都是 57bit 的,但是在 Xilinx 的 Ultraslace 架构下是 96bit 。

本视频将带您了解全新 Kria K26 SOM。专为加速视觉 AI 应用而构建,生产就绪型 K26 是在边缘部署自适应硬件的最快方法。Kria SOM 在设计时就考虑了软件工程师的需求,无需 FPGA 编程经验即可提供熟悉的设计环境,并由 KV260 低成本即用型开发工具包支持,轻松上手。

本文描述了Vivado仿真器作为独立工具和Vivado设计套件的一部分的使用,以及使用波形查看器来分析和调试设计。记录RTL设计的行为仿真,以及综合和实现设计的功能和时序仿真。

ECO 指的是 Engineering Change Order ,即工程变更指令。目的是为了在设计的后期,快速灵活地做小范围修改,从而尽可能的保持已经验证的功能和时序。ECO 是从 IC 设计领域继承而来,Vivado上 的 ECO 便相当于 ISE 上的 FPGA Editor。

DQ0-7 八根线必须连到同一T块(也称为字节组)上,一旦分在一起,这个字节组就不能放地址线和控制线了,只能放数据线。 每组数据线对应的DQS必须连到N6,N7上,也就是QBC或者是DBC上