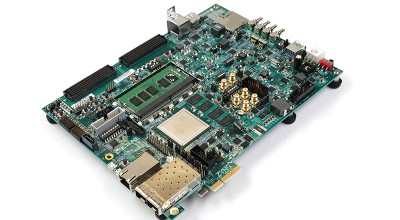

新致华桑推出基于Virtex UltraScale FPGA的第四代大规模原型验证系统

judy 在 周五, 04/30/2021 - 09:25 提交

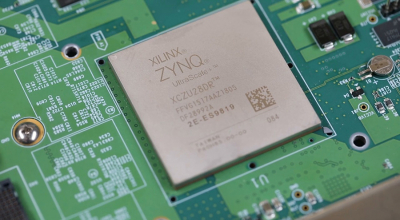

近年来,中国国内芯片市场发展迅速,而与之对应的芯片验证,仿真和测试的需求也急剧增加。Newtouch 希望借助最先进的FPGA 技术,升级其PHINEDesign FPGA 原型开发平台。该平台的前三代均基于赛灵思FPGA 平台而开发,其最近两代基于赛灵思Virtex®-7 2000T FPGA 和Virtex® UltraScale™ VU440 FPGA。