不断发展的数据中心 - 第二部分:Xilinx SmartNIC 如何改变数据中心(中文字幕)

judy 在 周三, 03/10/2021 - 09:19 提交

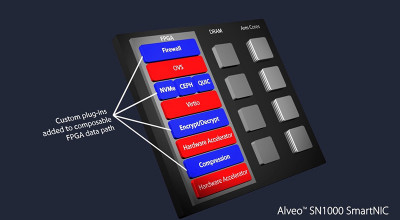

在本视频中,Xiinx 专家 Steven Pope 博士讨论了 Xilinx SmartNIC,以及全新软件可编程、硬件加速的 SmartNIC 如何改变数据中心。

在本视频中,Xiinx 专家 Steven Pope 博士讨论了 Xilinx SmartNIC,以及全新软件可编程、硬件加速的 SmartNIC 如何改变数据中心。

本文提供Versal™ ACAP编程和设计的软件专用信息。

手上的 Zynq 7020 单板带 HDMI 接口,Zynq 的 PS 并没有支持 HDMI IP 外设,所以再单板上的 HDMI 接口是直接接到了 PL 的引脚上,如果要用到 HDMI 来做为显示的话,那么就要在 PL 端去做一个 HDMI 协议层出来,既然要搞,那么需要先研究一下 HDMI 的协议

在本视频中,Xilinx 专家 Steven Pope 博士讨论了数据中心面临的挑战以及为什么常见的 SmartNIC 无法跟上数据中心的发展。

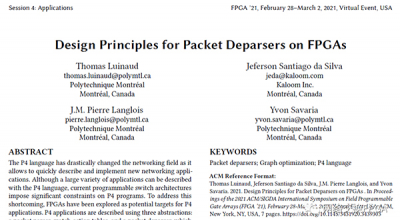

P4改变了网络格局,因为它允许表达自定义数据包处理。近年来,有几篇著作将P4程序映射到FPGA。但是,这些工作大部分都集中在实现数据包解析器或match action阶段。迄今为止,尚未有报道提出关于FPGA的通用数据包逆解析的原理。推荐一篇2021年FPGA顶会会议论文,介绍基于FPGA开源200Gbps数据包逆解析器的设计与实现。

ZC706中,MAC 控制器与 PHY 通过 RGMII(Reduced Gigabit Media Independent Interface)接口进行连接,实现千兆网。

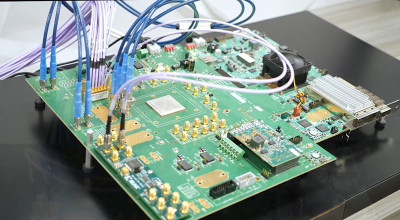

该演示展示了测试芯片收发器的基本工作情况,用一款 GUI 显示线路速率、均衡值和误码率(显示的性能比适用规范的要求高出几个数量级)。有了基于 ADC 的高级接收器和在 DSP 中实现的 DFE/FFE,该测试芯片和 GTM 收发器可支持各种协议,从超低损耗 OIF-CEI-112G-XSR 到诸如 100GBase-CR4 等高损耗线缆互连,不一而足。

在Vivado使用过程中,会碰到如下情况:设计代码已经编写完成,且仿真、综合或实现中的某一步骤已经通过,不需要再修改。此时可能需要添加一些注释代码,或者调整代码的格式,而任何修改都会导致状态更改为“Out of date”,提示用户更新设计。如何才能在不重新运行综合或实现的情况下解决这个问题?

SmartLynq +模块与 Versal ACAP 完美组合,可实现最佳生产力。本视频演示了通过高速调试端口(HSDP) 进行 Linux 下载有多快,并演示了 SmartLynq+ 模块提供的其他功能。