基于FPGA的超低延时硬件加速行情解析系统

judy 在 周四, 02/25/2021 - 09:50 提交

本文针对上海证券交易所的行情发布系统,采用Verilog硬件描述语言,在FPGA加速卡上开发了对行情信息流的以太网,IP和UDP以及FAST协议的硬件解码,设计了支持指令集编程的微指令加速引擎。与传统的基于软件的方法相比,本文提出的专用硬件处理方案延时可降低10倍以上。

本文针对上海证券交易所的行情发布系统,采用Verilog硬件描述语言,在FPGA加速卡上开发了对行情信息流的以太网,IP和UDP以及FAST协议的硬件解码,设计了支持指令集编程的微指令加速引擎。与传统的基于软件的方法相比,本文提出的专用硬件处理方案延时可降低10倍以上。

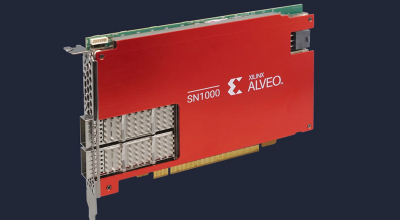

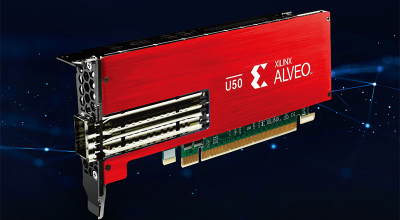

赛灵思今日宣布推出一系列全新数据中心产品及解决方案,包括全新Alveo SmartNIC系列、smart world(智能世界) AI视频分析应用、一款能够实现亚微秒级交易的加速算法交易参考设计,以及Xilinx App Store(应用商店)

基因工程技术已经成为当代生物技术领域的核心发展方向,伴随着人们对未知科学的深度探索和基础应用技术的不断发展,基因工程的研究已经涉足多类领域,比如诊断,精准医疗,农业,医药等。其中农业是目前基因分析及转基因应用研究最为广泛的领域之一。

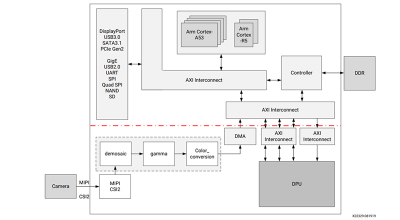

本文描述了Vitis™ AI开发包,这是一个用于深度学习处理器单元(DPU)的全栈深度学习SDK。

SmartNIC(智能网卡)到底是什么,它能做什么?基于DPU的SmartNIC不只是能实现网卡的连接作用,还实现了通常由CPU执行的网络流量处理。SmartNIC能够执行加密/解密、防火墙、TCP/IP和HTTP处理。本文从5个方面说明了为什么近年来SmartNIC的使用率一直在上升。

随着5G时代的到来,用户能直观感受到在网络电子产品上的应用会得到更多享受,智能化的3D技术、游戏、高清画质的视频与电影、直播互动都可以升级体验的娱乐方式,而以上应用对低时延要求的使用场景需要适应日益加快的生活节奏和人与网络间更高交互要求的挑战。

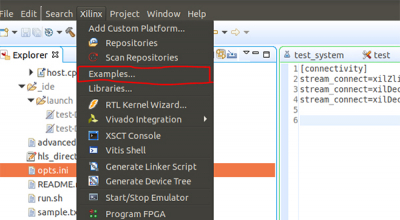

自从 Vitis 发布后,Xilinx 在 Github 上持续开源了很多资源,方便开发者进行自己的设计,减少产品上市时间。所以本期文章我们来看下如何获取和使用 Github 上的开放资源。

上一章梳理了一遍TVM前端流程,前端完成了tensorflow算子到TVM算子的转换。这一章CNN网络中最普遍的卷积运算为例,看一下relay算子的表示

赛灵思 Alveo 系列产品开发的视频 + AI 处理系统平台,使用分布式计算架构对视频处理进行设计及优化,在处理大规模视频流方面突破了 CPU 的瓶颈。对于直播流转码及音视频混合流任务,相对传统 X86 服务器,该系统在并发流量处理方面实现20-30倍的效率。

本文描述了用于卷积神经网络的 DPU。