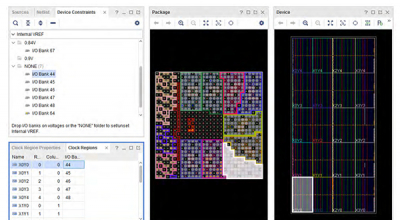

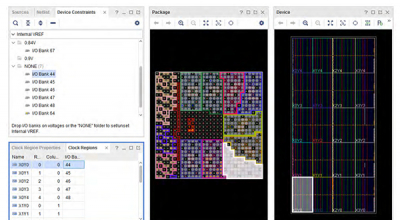

Vivado Design Suite 用户指南:I/O和时钟规划 (v2020.2)

judy 在 周二, 03/16/2021 - 15:00 提交

本文描述了I/O规划过程,在RTL设计中与PCB设计人员一起执行端口分配,并与系统工程师一起利用目标Xilinx FPGA上的时钟资源;使用Vivado设计套件减少内部和外部导线长度,提高系统性能。

本文描述了I/O规划过程,在RTL设计中与PCB设计人员一起执行端口分配,并与系统工程师一起利用目标Xilinx FPGA上的时钟资源;使用Vivado设计套件减少内部和外部导线长度,提高系统性能。

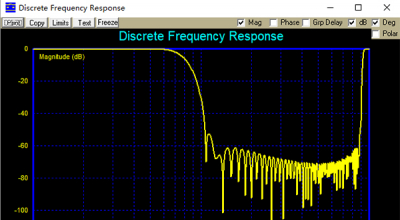

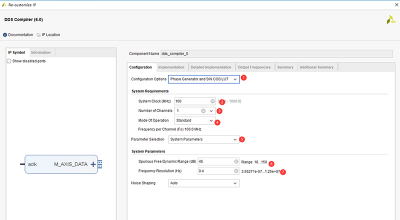

我们上一篇文章的混频是8MHz与5MHz的相乘,所以我们这篇文章的目的是设计一个低通滤波器滤除13MHz的成分。FIR的设计方法在数字信号处理中有两种方法,最常用的就是窗函数法。这里我们将使用汉明窗进行进一步的设计。

vivado提供了DDS IP核可以输出正余弦波形,配置方法如下

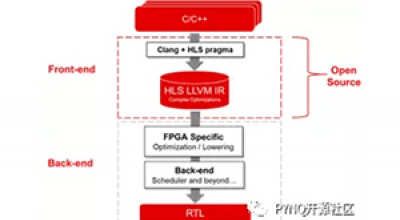

目前,虽然基于C/C++等高层次综合相较于手写RTL层级HDL语言已大幅提升了开发效率,但随着相关技术的不断进步,以及算法迭代的日益频繁,人们似乎并不满足于此。

不少刚刚接触到Pynq的用户第一个问号?Pynq是不是用Python编程FPGA的新物种?

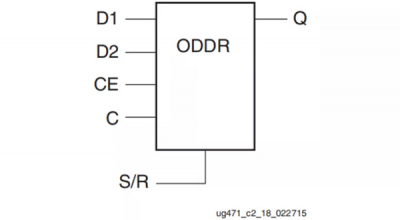

本文探讨一下ODDR用于时钟输出时的作用。

本文针对上海证券交易所的行情发布系统,采用Verilog硬件描述语言,在FPGA加速卡上开发了对行情信息流的以太网,IP和UDP以及FAST协议的硬件解码,设计了支持指令集编程的微指令加速引擎。与传统的基于软件的方法相比,本文提出的专用硬件处理方案延时可降低10倍以上。

在本视频中,Xilinx 高级总监兼数据中心系统架构师 Seong Kim 博士讨论了 Smart World 技术的需求以及 Xilinx 在解决关键实时应用方面的优势。

有很多客户在比较 FFT C-Model 仿真和 FFTIP 前仿遇到问题。今天赛灵思技术专家对此提出三种原因和解决办法。

在 v2020.2 中,针对 AXI 主接口引入了 Vitis HLS 自动接口扩展选项,了解如何与使用端口上的矢量数据类型来显式描述端口宽度进行比较。

本次项目我们主要是为了讲解DDS,所以我们使用了混频这个小项目来讲解。DDS自己手写是比较简单且灵活,但是Xilinx给我们提供了相应的IP核,那么这次我们将直接讲解使用IP来产生不同频率的正弦波