英文文档读不懂?Xilinx工程师帮你来翻译!

judy 在 周五, 12/04/2020 - 14:29 提交

不知道大家注意到了没有,赛灵思中文论坛多了一个新的板块。“赛灵思文档翻译理解”。看到这个名字大家会想,竟然有这么个专门的板块来翻译文档么?没错!各位小伙伴,今后我们这个板块就是专门来帮助大家翻译文档的。

不知道大家注意到了没有,赛灵思中文论坛多了一个新的板块。“赛灵思文档翻译理解”。看到这个名字大家会想,竟然有这么个专门的板块来翻译文档么?没错!各位小伙伴,今后我们这个板块就是专门来帮助大家翻译文档的。

DSP48E1片的数学部分由一个25位的预加器、2个25位、18位的补法器和3个48位的数据路径多路复用器(具有输出X、Y和Z)组成,然后是一个3输入加法器/减法器或2输入逻辑单元(参见图2-5)。使用2输入逻辑单元时,不能使用乘法器。

Vivado设计套件用户指南:编程和调试

JEDEC LPDDR4 规范 JESD209-4B 的最新发布版本引入了在每次写操作突发前后都将 DQS_c 驱动至高位并保持一段时间的要求(4.13 写操作和屏蔽写操作 DQS 控制信号(WDQS 控制信号)),其详情如下

DMA中断实例化函数,将要配置的DMA信息先lookupConfig再进行CfgInitialize,DMA采用块模式(Block mode),如果是Sg模式,则配置失败。定时器初始化函数,传入参数有定时器结构、加载值,设备ID。

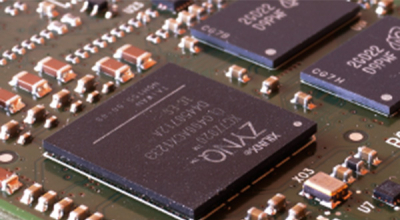

ZYNQ7000系列FPGA的PS自带两个IIC接口,接口PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35);SDK中需要对IIC接口进行初始化在黑金和米联的例程里为了方便用户使用,对IIC和外设设备分别创建了相应的文件方便用户开发。

赛灵思公司今天宣布已收购峰科计算解决方案公司( Falcon Computing Solutions ),这是一家为软件应用的硬件加速提供高层次综合( HLS )编译器优化技术的领先私人控股公司。此次收购将通过自动化硬件感知优化增强赛灵思 Vitis™ 统一软件平台,进一步降低软件开发者应用自适应计算的门槛。

在DSP48E1列中,级联各个DSP48E1片可以支持更高级的DSP功能。两个数据路径(ACOUT和BCOUT)和DSP48E1片输出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供级联功能。级联数据路径的能力在过滤器设计中很有用。

详细了解基于 Zynq UltraScale+ MPSoC 视频编解码器单元 (VCU) ROI 的编码参考设计的系统与硬件架构。 在详细了解硬件架构之前,先大概了解一下系统架构。 最后将介绍用于启动参考设计的资源。

本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。