PCIe系列第二讲、PCIe的OSI模型与事务层分析(上)

judy 在 周二, 06/30/2020 - 09:34 提交

PCIe协议定义了三层结构,分别是:物理层、数据链路层、事务层,每个层次按照协议中规定的内容,完成相应的数据处理功能,各层都分为发送和接收两功能块。在Xilinx芯片内部集成有PCIe硬核端点模块,能够自动完成数据链路层和物理层的数据处理

PCIe协议定义了三层结构,分别是:物理层、数据链路层、事务层,每个层次按照协议中规定的内容,完成相应的数据处理功能,各层都分为发送和接收两功能块。在Xilinx芯片内部集成有PCIe硬核端点模块,能够自动完成数据链路层和物理层的数据处理

PCIe2.0规范于2007年1月5日推出,将PCIe1.0 2.5GT/s的传输速率提高了一倍,每个通道的吞吐率从250MB/s上升到500MB/s,因此2通道的PCIe可支持高达1GB的总吞吐量。

Xilinx 7系列FPGA内置了一个模数转换模块,称为XADC。XADC内部集成了两个最高1MHz采样率,1Vpp的ADC模块,可以采集FPGA外部输入的模拟信号并转为数字信号。XADC不需要外接任何输入信号,就可以测量FPGA内部的温度,VCCINT,VCCBRAM,VCCAUX电压。

AXI4 从站接口将 AXI4 事务映射到 UI,以向内存控制器提供行业标准总线协议接口。UI 块向用户提供 FPGA 逻辑块。它通过呈现平面地址空间和缓冲读写数据来提供对本机接口的简单替代。

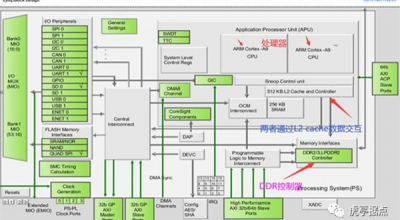

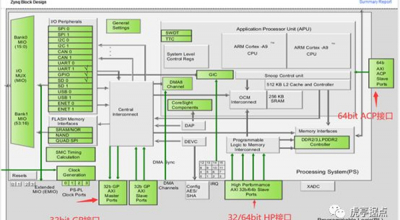

在ZYNQ的PS侧存在Cache,CPU与DDR之间通过Cache进行交互,数据暂存在Data cache中,在处理器对DDR进行写数据操作时,如果不将数据通过Cache送入DDR,DDR中的数据不会变化。在进行DMA操作时,如果没有对Cache进行适当的操作,可能导致以下两种错误

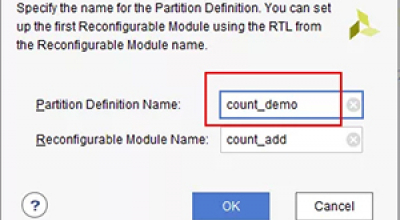

Partial Reconfiguration(部分重配置)在现在的FPGA应用中越来越常见,我们这次的教程以Project模式为例来说明部分重配置的操作过程。 这里我们使用的Vivado版本是2017.2,使用的例程是Vivado自带的wavegen工程,并在工程中增加一个计数器模块

DMA是一种内存访问技术,允许某些计算机内部的硬件子系统可以独立的直接读写内存,而不需要CPU介入处理,从而不需要CPU的大量中断负载,否则,CPU需要从来源把每一片段的数据复制到寄存器,然后在把他们再次写回到新的地方,在这个时间里,CPU就无法执行其他的任务

vivado 中使用modelsim联合仿真

Block RAM与Distributed RAM,简称为BRAM与DRAM, 要搞清楚两者的区别首先要了解FPGA的结构: FPGA=CLB + IOB+Block RAM CLB。一个CLB中包含2个Slice、8位寄存器、多路选择器、进位链等。

由于开发板DIGILENT Genesys2 的开发手册中说明了自带的时钟IP核为差分时钟,所以研究了下Vivado中差分时钟的配置方法