起飞!通过无线WIFI下载调试FPGA

judy 在 周一, 11/04/2024 - 09:30 提交

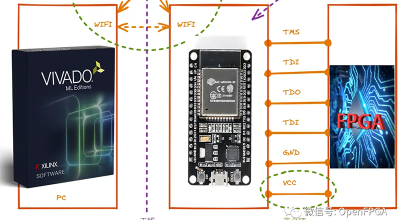

远程调试在整机调试时是很有必要和方便的,今天带给大家一个通过无线wifi下载调试fpga的一种方法

远程调试在整机调试时是很有必要和方便的,今天带给大家一个通过无线wifi下载调试fpga的一种方法

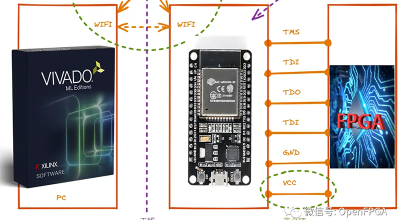

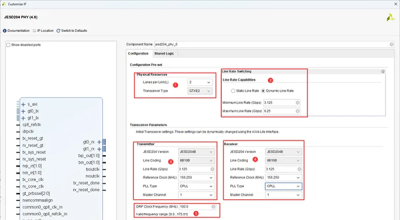

本文配置JESD204B PHY的参数,分析其示例工程,并且对该IP进行仿真,由于该IP只是物理层,并没有上层协议,因此与GTX/H其实没有太大区别。

本文将为你揭开寻找FPGA IP核和HDL模块资源的神秘面纱。

FPGA 允许在单个芯片中实现大量数字逻辑,其运行速度相对较高,并且只需很少或不需要在 CPU 内核上运行的传统顺序程序即可完成其工作。

延迟(Latency) 通常定义为信号从A点到B点所需要的总时长,单位通常是多少个时钟周期。

本文将带领大家深入了解FDATool,让滤波器设计变得简单而高效。

推荐一些国外大厂和高校的芯片设计参考资料,包括来自 Intel、ARM、Texas Instruments、MIT 等的材料,涵盖 Verilog/SystemVerilog、IC 设计和 FPGA 开发。

今天看的这篇论文,是一篇关于FPGA和ASIC在大模型推理加速和优化方向的综述,我们看下目前的研究进展。

带宽指频带宽度,是衡量微波系统能响应多少频谱的重要指标。从低频fL到高频fH之间的频率范围来计算

本次实验的物理层选择千兆以太网RJ45网口来验证该UDP协议栈的功能。首先将开发板的RJ45网口通过网线和PC连接,插入开发板的电源和下载器