JESD204B数据链路建立过程

judy 在 周四, 10/24/2024 - 09:41 提交

本文主要讲述JESD204B子类一的数据链路建立过程,后文讲解JESD204三种子类模式的链路建立,进而理解各种子类实现确定性延迟的方式。

本文主要讲述JESD204B子类一的数据链路建立过程,后文讲解JESD204三种子类模式的链路建立,进而理解各种子类实现确定性延迟的方式。

Xilinx®7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FPGA PCIe Gen3的应用接口及一些特性。

例化两个UDP协议栈模块,分别为主机A和主机B,主机A将用户端输入的数据打包,通过GMII接口发送给主机B

今天分享下数字信号处理中的“有限字长效应”。

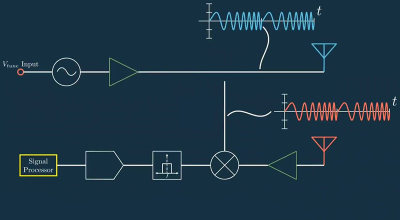

调频连续波(FMCW)雷达是现代汽车驾驶辅助系统的核心技术,包括自适应巡航控制、车道偏离警告和盲点监测等功能

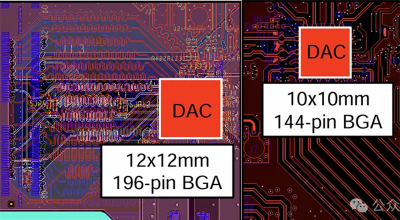

JESD204B是逻辑器件和高速ADC/DAC通信的一个串行接口协议,在此之前,ADC/DAC与逻辑器件交互的接口大致分为如下几种

该层在程序中为IP层的子层,设计了接收ICMP请求包并回复的功能

在本文中,我们将探讨 FPGA 如何通过推动自动化进步和突破机器人能力的界限来彻底改变机器人技术。

这篇文章我们介绍如何使用Python进行频率分析、噪声滤波和幅度谱提取。

inout端口信号在FPGA中应用还是很广泛的,特别是一些总线通信、数据交互的场景,比如i2c、spi等等。