从FPGA说起的深度学习(七)-循环并行化

judy 在 周一, 04/17/2023 - 10:01 提交

在本文中,我们将循环并行化应用于先前任务并行化的推理内核,并平衡层与层之间的执行时间

在本文中,我们将循环并行化应用于先前任务并行化的推理内核,并平衡层与层之间的执行时间

在设置input_delay时,我们经常会使用下面的方式

本文将介绍在Vivado中常用的TCL命令,并对其进行详细说明,并提供相应的操作示例。

这次选择中值滤波这个常规算法作为演示算法。算法原理很简单,我们先介绍均值滤波

这里介绍一种新的公平调度方案,和前面的方案相比,最大的特点是不缓存数据

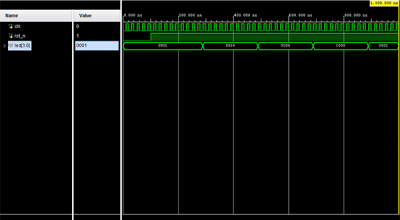

流水灯是大多数学习者接触到的第一个实验,也是非常经典的一个实验,在此,我们一起学习一下流水灯

vitis AI最近更新了3.0版本,对很多深度学习模型作了适配

VCS+Verdi的组合是EDA仿真中必备神器,以前只会用Vivado自带的仿真器或者Modelsim来进行仿真

本篇小文试着从一个SerDes用户的角度来理解SerDes是怎么设计的

在本文中,我们讨论一下I2C和SPI之间的区别