FPGA的版本管理

judy 在 周一, 02/27/2023 - 15:54 提交

搞FPGA的人可能都遇到过这样的问题:以前对外发布的版本的代码找不到了

搞FPGA的人可能都遇到过这样的问题:以前对外发布的版本的代码找不到了

传递的 Mixer/NCO 设置用于更新相应的块级寄存器。 使用新值更新驱动程序结构体

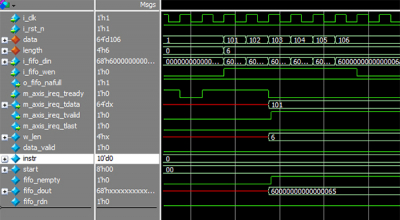

本文写AXI4-Full接口。AXI4-Full接口的源码基本与AXI4-Lite接口的源码一致

在 Linux 系统中,在众多的指令中,对于 FPGA/IC 开发设计人员来说,使用指令最多的就是对文件和目录进行操作

本文主要介绍关于RF数据转换器的ADC和DAC均适用的状态指示函数的相关使用方法

IP报文的头部中有一个checksum字段,一般都知道这个字段的含义

这篇文章主要介绍了 Verilog 在 FPGA 设计中的概念和使用方法

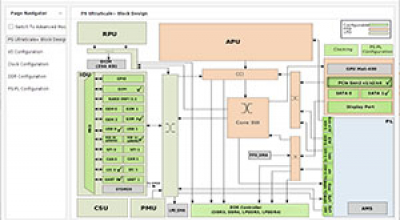

1、建立工程,2、编译工程,导出xsa文件,3、建立petalinux工程

srio 的IQ接口都是基于axistream的,以前没怎么用过axistream的接口

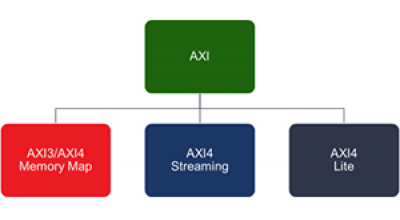

AXI 表示 Advanced eXtensible Interface(高级可扩展接口),它是由 Arm 定义的接口协议