FPGA ISP SmartBlur去噪

judy 在 周五, 02/03/2023 - 09:36 提交

这个算法对图像有一定的包边去噪效果,在FPGA上实现起来复杂度较低

这个算法对图像有一定的包边去噪效果,在FPGA上实现起来复杂度较低

本文概述了如何在系统中使用RFSoC 射频数据转换器的多块同步功能。

PCB设计人员可以使用本章中的分析和示例来辅助此类通道的设计

最近看手底下的小伙子们写代码,对于跨时钟域的处理极度的不规范

重定时和流水线是强大的技术,广泛应用于当今的 FPGA 综合工具中

本文主要对RFSOC的上电顺序、TDD 模式、比特流重配置等内容进行介绍

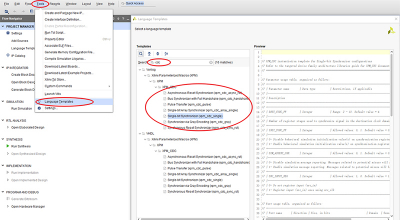

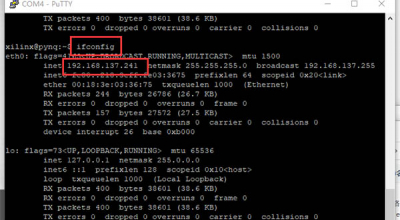

打开控制面板-网络与Internet-更改适配器设置-选择需要共享的网络

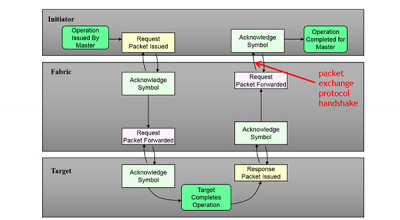

SRIO的协议有一千来页,一个初学者是不可能一开始就去读协议的

本文提供了一些管理信号衰减的指南,以便为给定的应用获得最佳性能

在设计中的关键路径发现某个寄存器具有高扇出和高延迟时,使用寄存器复制是个不错的实现时序收敛的方法