从底层结构开始学习FPGA——时钟结构

judy 在 周三, 07/20/2022 - 09:04 提交

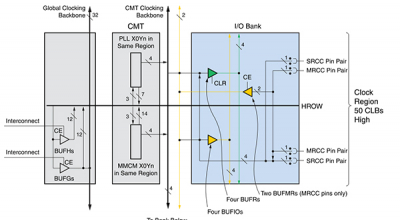

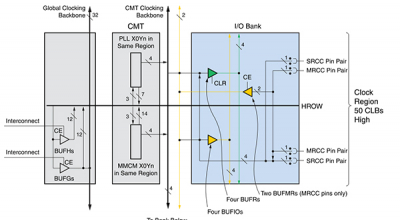

7系列FPGA的时钟资源通过专用的全局和区域I/O和时钟资源管理复杂和简单的时钟需求。

7系列FPGA的时钟资源通过专用的全局和区域I/O和时钟资源管理复杂和简单的时钟需求。

7系列FPGA支持非常宽的I/O电压标准,本文介绍以下典型的I/O电压标准及端接匹配电路

在进行FPGA开发时,常用的代码编辑器比如Sublime,但是最近发现再Sublime中编辑的代码文字部分

之前通过发布的文章是真实的(文章是描述的)命令命令在上面的实际情况下使用的。在实现的每个子结束后打印至指定日志文件

在这篇文章中,已经对FIFO IP核的各个关键因素做了详细的讲解。

本文介绍如何使用K26 SOM新建最小系统,以及如何解决工程中经常出现的问题。

本节介绍最简单的实验工程,用串口打印helloworld。

本文对xilinx FIFO IP的参数做详细解读

MicroBlaze具有多功能互连系统,可支持各种嵌入式应用。

从本文开始我们介绍Xilinx 7系列FPGA的SelectIO资源结构及使用