作者:AMD 工程师 Simreet Behera & Abhinav Dubey

本文主要介绍了 AMD Vivado™ IP integrator (IPI) 的诸多功能特性。我们将讲解 Vivado IP integrator 的各项基本功能,欲知详情,请参阅以下 GitHub 仓库中所含教程:

https://github.com/Xilinx/Vivado-Design-Tutorials/tree/2022.1/Design_Flow_Tutorials/IP_Integrator

我们还将带您了解在 AMD Zynq™ UltraScale+™ MPSoC 开发板与 AMD Versal™ 自适应 SoC 开发板上使用 IP integrator 时,两种设计流程之间存在的差异。

除此之外,我们将介绍块设计容器 (BDC),最后是介绍“Module Referencing”(模块引用)功能,该功能可用于将 AMD IP (XCI)、RTL 设计或块设计 (BD) 例化到另一个 BD 中。

IPI 的基本功能特性

我们将在基于微处理器的设计中使用 AMD Zynq UltraScale+ MPSoC 开发板来介绍 Vivado IPI 的基本功能特性,如从 IP 目录添加 IP、运行连接自动化、块自动化设置、创建层级和使用地址编辑器。

在 IPI 中,基于微处理器的设计流程如下:

1. 从 Vivado IP 目录添加 IP

微处理器 IP

根据您的设计规范,将相关 IP 添加到新的块设计 (BD) 中,如 MicroBlaze 处理器 IP、Zynq 处理器系统 IP 等

互连 IP

AXI Interconnect、AXI Smart Connect 等存储器接口 IP

PS DDR4 Controller、AXI Block RAM (BRAM) Controller 等接口 IP

AXI General Purpose Input/Output (GPIO)、AXI UART_lite 等

2. 使用设计辅助功能

IP integrator 提供了一项名为“Designer Assistance”(设计辅助)的功能,其中包含“Connection Automation”(自动连接)、“Block Automation”(块自动化设置)和“Board Automation”(板自动化设置)。它能帮助您在不同块之间建立内部连接以及建立从各块到外部接口的连接,从而组建一个基本 IP 子系统。在设计中使用 AMD MicroBlaze™ 处理器或 Zynq UltraScale+ MPSoC (Zynq_ultra_ps_e_0) 等嵌入式处理器时,就会提供“Block Automation”功能。

如果使用开发板(如 ZCU102 评估板)来创建工程,则“Board Automation”功能可协助将 IP 接口连接到外部开发板。由于所选开发板的所有 I/O 管脚分配和属性都已固定,因此该功能还会处理这些分配和属性。

例如,在 MicroBlaze 设计中,“Connection Automation”功能将帮助您完成 UART 和 GPIO 接口的连接以及 AXI BRAM Controller 到 Block Memory Generator 的连接。

3. 创建层级

您可运用多种不同方法来更改画布上的视图,以便对各块进行更妥善的组织。其中有一项功能是创建层次结构,用于对一个或多个块进行分组。层次结构不仅有助于对画布上的块进行组织,还能对块设计的不同部分进行复制。例如,您可以按住 Ctrl 键并逐一点击 microblaze_0、microblaze_0_local_memory 和 mdm_1 块来创建一个层次结构。

4. 在 IPI 中标记信号以供调试

IP integrator 中的 System ILA 调试核支持您对块设计执行系统内调试。需要监控设计内的接口和信号时,即可使用此功能。

如下图所示,您只需右键单击信号线并从上下文菜单中选择“Debug”(调试),即可标记 AXI SmartConnect 与 AXI GPIO IP 之间的接口。

5. 创建和实现顶层设计

完成 IP 子系统设计后,您可将其作为模块或块包含在顶层设计内,也可以将其用作为顶层设计本身。但无论如何,您都需要为子系统设计生成 HDL 文件。这是通过生成输出文件完成的,随后会为设计启动中的每个 IP 运行非关联 (OOC) 流程。然后,您将创建 HDL 封装文件,并为设计生成比特流。该步骤包括了综合与实现。

如需了解更多信息,请参阅《Vivado Design Suite 用户指南:采用 IP integrator 设计 IP 子系统》(UG994):

https://docs.amd.com/r/en-US/ug994-vivado-ip-subsystems

使用 IP integrator 完成基本 Versal 设计

AMD Versal 自适应 SoC 计算加速平台包含多个处理器,每个处理器都具有不同的计算功能用以满足各种应用需求。所有器件都包括处理器系统 (PS) 和平台管理控制器 (PMC)。此外还包括片上网络 (NoC) 互连,用于支持所有处理器接入 DDR 存储器控制器以及器件内的其他资源。

Versal 自适应 SoC 支持 2 种设计流程:传统设计流程和基于平台的设计流程。

本文我们将重点介绍传统设计流程,因为这种设计仅由 RTL 和 IP 组成。

一个基本的 Versal 设计涉及通过配置 Control, Interface, and Processing System (CIPS) IP 核来选择合适的启动器件和外设。这对于 Versal 设计至关重要,因为平台管理控制器 (PMC) 整合在 CIPS IP 中,必须配置 PMC 才能让 Versal 器件正确启动。此外,硬化的 DDR 存储器控制器 (DDRMC) 只能通过 NoC IP 来访问。要使用硬化的 DDR 存储器控制器,您的设计应包含 NoC IP。

您可根据自己的需要通过 CIPS 自定义 GUI 来自定义 CIPS。例如,您可以更改 QSPI 模式、启动模式,设置适当的 I/O 管脚等。

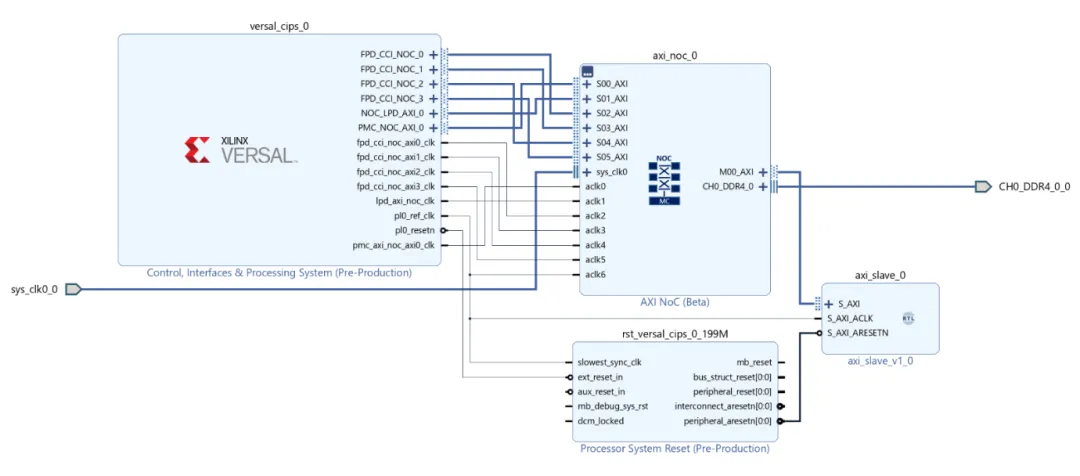

以下是包含 AXI NoC IP 的基本 Versal 设计的截图:

您可以对这个设计执行“Save”(保存)、“Validate”(确认)和“Implement”(实现),最后生成比特流(PDI 文件),用于烧录 Versal 开发板。

如需了解有关 Versal 设计流程的更多信息,请参阅《Versal 自适应 SoC 设计指南》(UG1273):

https://docs.amd.com/r/zh-CN/ug1273-versal-acap-design/%E6%A6%82%E8%BF%B0

基本 Zynq UltraScale+ MPSoC 设计与 Versal 设计之间的差异

使用 Zynq UltraScale+ MPSoC 开发板进行设计与 Versal 开发板进行设计相比,有些设计注意事项需要考量。下表提到了这两种架构在设计上的一些差异。

如需了解有关这两种架构的更多信息,请参阅《Versal 自适应 SoC 技术参考手册》 (AM011):

https://docs.amd.com/r/en-US/am011-versal-acap-trm

和《Zynq UltraScale+ 器件 TRM》(UG1085):

https://docs.amd.com/v/u/en-US/ug1085-zynq-ultrascale-trm

块设计容器简介

块设计容器 (BDC) 扩展了 Vivado IP integrator 的分层块功能。如果块设计 (BD) 可包含用户选定的 IP 块且数量不限,那么分层块能用于在该设计层级内创建新的层次。块设计容器 (BDC) 功能特性会将分层块及其中所含内容转变为单独的块设计 (BD) 本身。生成的块设计定义为 BD 设计源文件,并且也可在其他块设计工程内使用。使用 BDC 的好处在于,父 BD 与子 BD 之间的边界是透明的。例如,参数传输和地址分配都可以通过这个层级来完成。

BDC 同时支持自上而下的设计流程和自下而上的设计流程。

自上而下流程

在自上而下流程中,首先会创建顶层块设计的流程图,然后按适当的层级将一组 IP 块作为子块推送到 BDC 内。借助外部接口和特定功能块的详细信息,即可构建和验证顶层 BD。随后,设计团队可以复用该顶层 BD 来开发其 BDC 部分。在为所有团队成员复制单个工程或者处理以相同器件为目标的多个工程的过程中即可完成此操作。

自下而上流程

在自下而上设计流程中,子块设计是单独创建的,您需要在顶层块设计中将这些子块作为 BDC 来加以例化。团队成员可以集中精力为所分配的设计分区开发 BD,以便在顶层 BD 中将该 BD 作为 BDC 来加以复用,或后续在另一个工程中一起复用。

IPI 中的模块引用

IP integrator 的模块引用 (ModuleRef) 功能特性支持您快速将来自 Verilog 或 VHDL 源文件的模块或实体定义直接添加到自己的块设计中。此方法支持快速添加 RTL 模块,无需将 RTL 封装为 IP 再通过 Vivado IP 目录来添加。

模块引用流程很快,但不具备下列使用 IP 目录来处理时所具备的优势,如:

1. 提供精确定义的 IP,可通过 IP 目录来管理

2. 能够在多个设计中使用这些 IP

3. 能够在有新版本 IP 可用时进行升级

您可为块设计、XCI 文件和 RTL 模块创建模块引用。

要在不同 BD 中使用 IP 或 BD 模块引用功能,您必须首先创建 AI 引擎接口拼块 RTL 文件。AI 引擎接口拼块文件只是 RTL 模块/封装文件,必须将其作为工程源文件添加到设计中,此文件充当“挂钩”用于连接工程要引用的其他 IP 或 BD 源文件。您可以从 IP 或 BD 例化模板或者从生成的 BD 封装文件中创建一个新的 AI 引擎接口拼块 RTL 文件(例如:包含“shim”模块的 shim.v)。

例如,将 MicroBlaze 处理器 IP 例化到另一个 BD 内时,所用的 shim.v 文件如下所示:

限制

1. ModuleRef 不得包含 CIPS 或 NoC IP。

2. ModuleRef 无法例化一个或多个 DCP 模块。

3. ModuleRef 无法例化一个或多个 ModuleRef(即“嵌套 ModuleRef”)。

4. ModuleRef 无法使用块设计容器 (BDC) 技术来例化 BD。

结论

在本篇博文中,我们了解了如何利用 IP integrator 的众多功能特性来创建基本的 MicroBlaze 设计和 Versal 设计,并观察了这两种设计流程之间的差异。

我们还谈及如何通过 2 种受支持的块设计容器流程(自上而下流程和自下而上流程)来扩展 IPI 的分层功能。

最后,我们讲解了全新的模块引用功能特性,它支持您快速将来自 Verilog 或 VHDL 源文件的模块或实体定义直接添加到自己的块设计中。