作者:Herbert,来源:易灵思官微

在 RISC-V 架构的复杂体系中,寄存器扮演着关键角色。易灵思 Sapphire SoC 以对 RISC-V 软核及硬核的有力支持,备受关注。本篇文章旨在描述易灵思 Sapphire Soc(软核)、Sapphire HP Soc(硬核)按照 RISC-V 标准规范中的 mcause 、mstatus 寄存器的工作逻辑。这在日常软件调试和底层系统开发中,具有重要作用。

1. 核心概念:特权级与陷入机制

mstatus 和 mcause 是 RISC-V 特权架构的核心,是实现操作系统安全、管理系统状态以及响应事件的基石。

1.1 RISC-V 特权模型

RISC-V 定义了分层的特权模型,为软件组件提供保护屏障。主要包含三个特权级别:

用户/应用模式 (U-mode): 权限最低,运行常规应用程序。 监管者模式 (S-mode): 权限较高,为操作系统内核设计。 机器模式 (M-mode): 拥有最高权限,可完全访问硬件,是唯一强制必须实现的特权级别。

任何从低特权级尝试执行高特权级操作的行为都会引发一个陷入(trap),将控制权转移给更高权限的软件处理。

Sapphire / HP Soc 均完整实现了这三种工作模式,均能完美运行各类现代操作系统,如 Linux。

1.2 陷入机制 (Trap)

“陷入”指因异常或外部事件导致程序控制流意外转移至陷阱处理程序的过程。陷入分为两大类:

异常 (Exceptions): 同步事件,是执行指令的直接后果,如非法指令或系统调用(ECALL)。 中断 (Interrupts): 异步事件,与当前指令流无关,如定时器到期。

RISC-V 采用统一的陷入处理机制,所有事件都引导至单一的处理流程,简化了硬件设计。

mcause 寄存器的作用就是让软件能够精确区分导致陷入的具体事件。

当陷入发生时,硬件的副作用被严格限制在更新少数几个关键的控制与状态寄存器(CSRs),如 mstatus, mcause, mepc 等,并改变程序计数器(PC)。RISC-V 硬件不负责保存通用寄存器,这一任务完全由 M-mode 的陷入处理程序软件完成,这赋予了软件极大的灵活性。

2. 机器状态寄存器 (mstatus)

mstatus 寄存器是控制处理器核心(hart)运行状态的最关键 CSR,如同处理器的“主控制开关”,其管辖范围覆盖了中断使能到内存访问权限。

2.1 概述与核心功能

对于 RV32 架构,mstatus 是一个 32 位的可读写寄存器,用于跟踪和控制 hart 的当前操作状态。它的一个受限子集以 sstatus 寄存器的形式暴露给 S-mode。mstatus 维护处理器的全局状态,包括全局中断使能、陷入前的特权级别以及扩展(如浮点单元)的上下文状态。

2.2 RV32 mstatus 寄存器位域详解

下表详细列出了 mstatus 在 RV32 架构下的位域布局和功能描述。

表 1: RV32 mstatus 寄存器位域布局与描述

在易灵思 RISC-V IDE 中,大家最长打交道的寄存器,如程序中断程序初始化,先要通过 csr_write 操作来配置该寄存器的标志位。

2.2.1 中断与特权级栈 (MIE, MPIE, MPP 等)

mstatus 包含两对关键的栈式字段,用于在陷入时自动保存和在返回时自动恢复处理器状态:

中断使能栈 (MIE/MPIE, SIE/SPIE): 当陷入 M-mode 时,硬件会自动将当前 MIE 位的值保存到 MPIE,然后将 MIE 清零以禁用中断。执行 mret 指令时,硬件会从 MPIE 恢复 MIE 的值。这确保了陷入处理程序在中断屏蔽的安全环境中开始执行。 特权级栈 (MPP, SPP): 当陷入 M-mode 时,硬件会自动将发生陷入时的特权级保存在 MPP 字段中。执行 mret 指令时,处理器会读取 MPP 字段的值,以决定应返回到哪个特权级。

2.2.2 扩展上下文状态 (FS, SD)

FS(浮点状态)和 SD(状态脏位)字段用于实现“惰性状态保存”优化。硬件会自动跟踪浮点单元(FPU)的状态,当 FPU 寄存器被修改时,会将 FS 字段置为 Dirty (11)。操作系统在上下文切换时,只需检查 mstatus.FS 或更快速的 mstatus.SD 位。如果状态不是 Dirty,就可以跳过保存 FPU 寄存器的昂贵操作,从而显著提升性能。

浮点 Dirty 标志也是重要的功能,在易灵思实现的 FreeRTOS 移植中,使用了该方法来提供快速切换,从而不需要每次切换堆栈的时候都保存所有浮点寄存器。

3. 机器原因寄存器 (mcause)

mcause 是陷入机制的“诊断仪”,它告诉软件是什么事件导致了陷入。

3.1 目的与结构

mcause 是一个 32 位寄存器,包含一个代码,指明导致陷入的事件。

中断位 (Interrupt Bit): 最高位(第 31 位)。若为 1,表示陷入是异步中断;若为 0,表示是同步异常。 异常码字段 (Exception Code Field): 低 31 位包含一个数值代码,标识具体的中断或异常类型。

3.2 机器模式陷入原因代码表

表 2: 机器模式同步异常代码 (RV32)

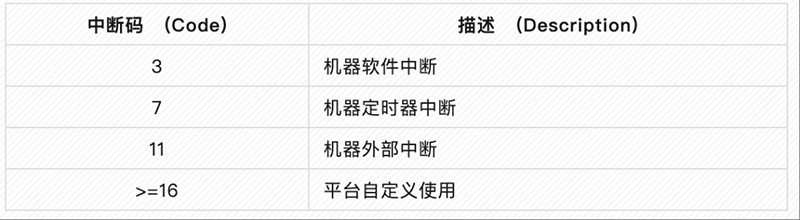

表 3: 机器模式中断代码 (RV32)

陷入生命周期:mstatus 与 mcause 的协同

4.1 阶段一:陷入进入 - 硬件原子操作

当陷入被 M-mode 捕获时,硬件会执行一系列原子操作:

将 PC 保存到 mepc(机器异常程序计数器)。 将原因代码写入 mcause。 将故障相关信息(如地址)写入 mtval。 在 mstatus 中:将当前特权级存入 MPP,将 MIE 存入 MPIE,然后将 MIE 清零。 将 PC 更新为 mtvec(机器陷入向量)指定的地址,跳转至处理程序。

表 4: 进入 M-mode 陷入期间 CSR 状态变化总结

4.2 阶段二:陷入处理 - 软件响应

软件陷入处理程序从 mtvec 地址开始执行。典型步骤包括:

保存上下文:使用 mscratch 寄存器预存的内核栈指针,将通用寄存器等保存到安全的内存区域。 诊断与服务:读取 mcause、mepc 和 mtval,根据原因代码跳转到相应的服务例程。 准备返回:从栈中恢复之前保存的上下文。

mret 指令用于从 M-mode 陷入中返回。它执行与陷入进入时相反的原子操作 :

将特权级恢复为 mstatus.MPP 的值。 将 mstatus.MIE 恢复为 mstatus.MPIE 的值。 将 mstatus.MPIE 置 1。 将 PC 恢复为 mepc 的值。

总结

mstatus 和 mcause 是 RISC-V 特权架构的两个核心支柱。mstatus 是 hart 的控制平面,负责管理其运行状态、中断策略和内存权限。mcause 则是陷入机制的诊断核心,为处理异常事件提供必要的原因信息。

在支持 S-mode 的系统中,还可以通过 medeleg 和 mideleg 寄存器将特定的异常和中断委托给 S-mode 直接处理,从而避免进入 M-mode 的开销,提升系统性能。当陷入被委托时,硬件会更新 S-mode 对应的 scause、sepc 等寄存器,而 mcause 等 M-mode 寄存器则不会被触动。

总而言之,这两个寄存器共同构成了一个简洁、优雅且功能强大的基础,深刻反映了 RISC-V 通过明确的硬件机制赋予软件最大灵活性的设计哲学。

易灵思Sapphire/Sapphire HP Soc,是完整实现了RV32IMACD指令规范的CPU,CSR寄存器作为RISCV的核心,对于系统实现,软件生态存在着至关重要的作用,从生态兼容的角度而言,也为行业节约了使用成本,提供了敏捷的开发速度。