作者:Brian Liu,来源:FPGA FAE技术分享选集

AMD FPGA的热设计是确保器件稳定工作、延长寿命并优化功耗的关键环节。FPGA 的热特性与其功耗、封装类型、环境温度及散热方案密切相关际应用场景综合设计。

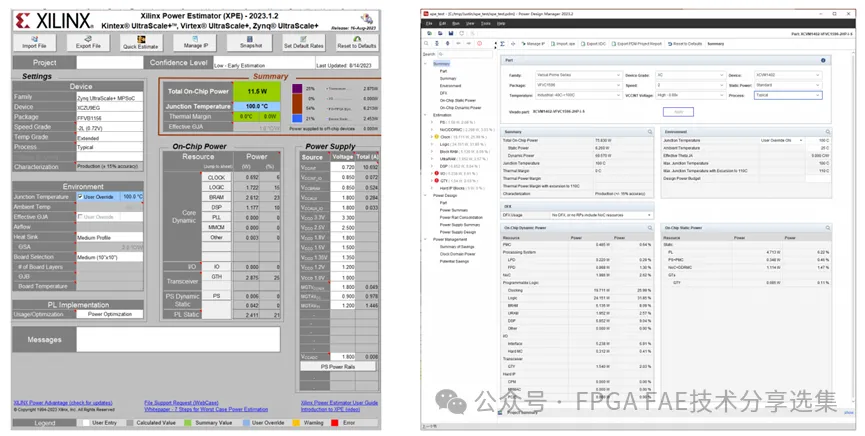

一个完整的电源/热管理/板级设计方法的框图如下图所示:

AMD提供功耗评估、热模型等多种工具。

功耗评估工具:

参考官方文档:XAPP1377: Designing Heatsinks and Thermal Solutions for Xilinx Devices 有详细的设计热系统的步骤,包括:

A. 确定包装盖类型和相关文档。

B. 确定包装的接触面积和高度要求。

C. 设计散热器底座。

D. 设计散热片和气流方向(如果是液体冷却,则为流体流量)。

E. 设计正确的周边配件。

F. 选择最佳的热界面材料(TIM) 并确定应用。TIM 是设备和热堆叠在一起的物质,旨在改善热接触。

G. 确定用于仿真的热参数并验证热。

H. 确定正确的组装、测试和调试(如有必要)。

封装上,如果选择Lidless Packaging也会对散热有优势。

无盖设备的热性能更优,这是因为其RJC(结到壳的热阻Thermal Resistance from Junction to Case)值更低。相较于有盖式设备,其结温更低;

提高了散热解决方案的效率;降低了静态功耗或允许更高的工作环境温度。

对于其他外围器件的选型,尽量精简或选择低功耗器件。

比如DDR的设计,在带宽满足的情况下,使用LPDDR4替代DDR4。LPDDR4 相比 DDR4 的功耗节省在同等带宽下幅度普遍在30%~50%,尤其在轻负载和待机场景下优势更大。这也是其在移动设备、边缘计算、低功耗嵌入式系统中替代 DDR4 的核心原因。

MPSoC 的 PS 端采用多电源域设计,可通过关闭或降频闲置域的电源来减少静态功耗:

PS_VCC:核心处理器(A53、R5)及逻辑电路。

PS_VCCIO:I/O 接口(如 GPIO、UART、SPI)的电源。

PS_VCC_PLL:PLL 时钟电源。

PS_VCC_DDR:DDR/LPDDR 控制器电源。

可通过 PMU(Power Management Unit)或外部电源管理芯片(如 PMIC)关闭闲置域电源,例如:若不使用 R5 处理器,可关闭其电源域(需通过 PS 的电源管理寄存器配置);未使用的 I/O Bank(如未连接外设的 GPIO 组)可关闭对应PS_VCCIO电源。

处理器核开关与降频也能大幅节省功耗,A53支持对称多处理(SMP),轻负载时可关闭部分核心;降低 A53/R5 的时钟频率;启用处理器空闲状态(如 ARM 的 WFI/WFE 指令),让核心进入低功耗模式。

对外设的优化:比如DDR降频;PHY 芯片(如以太网PHY、HDMI PHY等)闲置时关闭收发器。

时钟网络优化(动态功耗的主要来源):

利用 Xilinx 专用时钟门控单元(如BUFGCE、LUT-based gate)对空闲模块关闭时钟。例如,用BUFGCE控制高频时钟的分发。

时钟频率与分频:

按模块需求分配最低必要频率:非关键路径(如低速接口、状态机)使用分频时钟,避免 “一钟到底”。例如,用MMCM生成多档频率(100MHz 核心逻辑、25MHz 外设接口)。

避免过度设计时钟频率:若时序分析显示存在较大裕量(Slack),可降低时钟频率(如从 200MHz 降至 180MHz),动态功耗随频率线性降低。

合并时钟,尽量少用到MMCM,每个MMCM在MSoC上可能多消耗100mw左右的功耗。

IO驱动:

A. 在满足性能的前提下,IO驱动电流通过约束降低,比如由12ma改为8ma;

set_property DRIVE 8 [get_ports {data_out}];

B. IO驱动斜率改为slow

set_property SLEW SLOW [get_ports {data_out}]。

减少时钟缓冲与扇出:

避免不必要的全局时钟缓冲(BUFG):局部时钟(如小模块内的分频时钟)可使用区域缓冲(BUFR),减少全局布线负载。

拆分高扇出时钟:若时钟驱动大量寄存器,可拆分时钟树为多个子树(通过多个BUFGCE),分别控制使能,降低时钟的负载。

资源复用:

多个模块共享一个 DSP48(如时分复用乘法器),减少资源实例化数量(资源越多,静态功耗越高);小容量存储优先使用 BRAM(块 RAM)而非 LUT 构成的分布式 RAM,BRAM 的功耗密度(功耗/bit)更低,且布线更集中。

Transceiver摆幅:

六、Vivado工具优化手段

综合阶段(Synthesis)优化

综合阶段将 RTL 代码转换为门级网表,合理配置综合策略可减少冗余逻辑、优化资源利用,为后续实现阶段奠定基础。

Vivado提供预设综合策略,针对不同目标(功耗、性能、面积)优化:

根据设计选择最合适的策略。

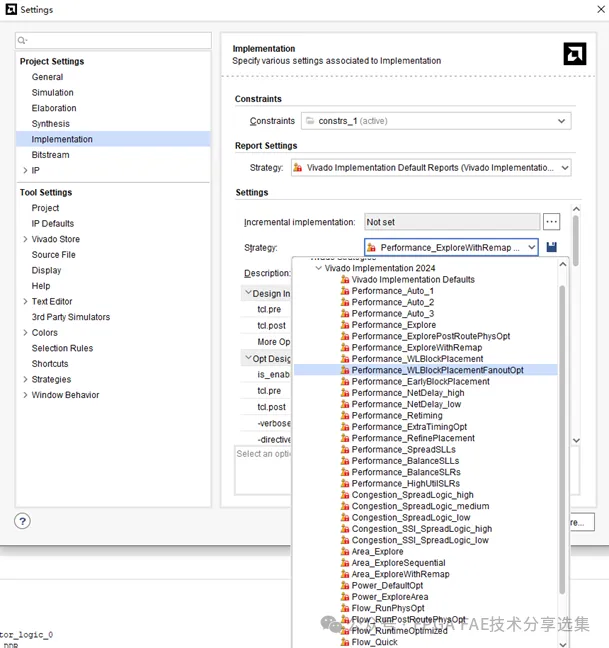

实现阶段(Implementation)优化

Opt Design(逻辑优化)

对设计进行逻辑级优化,包括逻辑重定时、资源共享、冗余逻辑删除等,为后续布局布线奠定基础。-directive 设为 Default 是通用优化策略,可根据设计目标(如性能、面积、功耗)切换为对应的专项策略(如 AreaOptimized PerfOptimized 等)。

Power Opt Design(功耗优化)

专门针对功耗进行优化,通过调整逻辑结构、减少信号翻转率等方式降低动态功耗和静态功耗。is_enabled 勾选,表明当前设计启用了功耗优化流程,这会让工具在逻辑优化阶段额外加入功耗驱动的算法,在满足时序的前提下尽可能降低功耗。这种配置适合对功耗敏感的 FPGA 设计(如电池供电设备、边缘计算场景),通过同时启用通用逻辑优化和专项功耗优化,可在性能与功耗之间取得较好平衡。

最终的时序状况对功耗也会有较大的影响,通过 Vivado 的report_power和report_timing联合分析,定位 “高功耗且时序裕量充足” 的模块,对其放松时序约束或优化逻辑结构。比如某模块时序裕量为 10ns,功耗占比 15%,可通过降低其时钟频率或增加门控来减少功耗。总的来说,需要避免过度时序约束,按实际需求设定频率和路径延迟;对不同模块划分时钟域,高频时钟仅用于关键路径,低频时钟用于非关键模块;

通过这种协同设计,可在保证性能的同时达到降低功耗的目的。

参考文档:

1. AMD技术专家李进华《High-reliability Hardware Design》。

2. AMD技术专家顾永国《Power reduction》。

如果您有FPGA功耗优化相关问题,欢迎联系: