作者:Nicholas,来源:易灵思官微

RISC-V(Reduced Instruction Set Computing-V)是一个开源指令集架构(ISA),它的设计目标是提供一个简洁、可扩展且高效的指令集,适用于各种应用场景,从低功耗设备到高性能计算。易灵思提供完整的RISC-V 解决方案,致力于让开发者和硬件设计人员可以根据需要自定义和扩展指令集,且无需担心专有技术的限制。

RISC-V的特点:

简洁高效:RISC-V采用精简的指令集,使得每条指令的执行时间更短,提高了处理器的性能。 模块化设计:RISC-V支持通过扩展来增强处理器功能,比如加速浮点运算、增加原子操作指令等。 开源免费:RISC-V的开源性质允许任何人使用、修改和扩展指令集,降低了硬件开发的成本。 可定制性强:用户可以根据实际应用需求,添加或删除指令、修改处理器架构。

易灵思提供的RISC-V IP支持用户自定义指令。众所周知,自定义指令不仅能够提升特定算法的执行效率,尤其是在涉及到计算密集型或硬件加速任务时,尤其重要。例如,在数字信号处理(DSP)、图像处理或加密解密等应用中,自定义指令能够显著提高处理速度,并降低处理延迟。通过使用易灵思的Sapphire RISC-V SoC IP核,开发者可以灵活配置和生成支持自定义指令的系统设计,充分利用FPGA硬件资源进行定制化加速。这样的设计不仅满足了高性能计算的需求,也降低了开发复杂度和硬件成本。

本次讲给大家介绍易灵思RISCV的自定义指令:

在Sapphire RISC-V SoC中,支持用户定义的自定义指令,这使得开发者能够加速特定的计算任务。自定义指令接口支持R型指令格式,并通过两个寄存器(rs1 和 rs2)向自定义硬件逻辑传输数据。用户可以定义最多1024个ID,每个ID对应一个特定的功能。

接下来我们先看一下R指令的格式:

上图是RISC-V手册中的基础的指令,我们需要重点看一下R指令格式,其中bit6:0是opcode,bit11:7是rd——作为输出,bit14:12是function3,bit19:15是rs1,bit24:20是rs2,bit31:25是function7。

其中function3和function7共10bit,因此支持1024个功能ID。

自定义指令的使用方法:

RISCV DIE中定义指令:用户可以通过定义一个特定的功能ID来指定指令的行为。

FPGA测处理 对应的接口信号:

cmd_valid:指令是否有效,表明指令数据已经准备好。

cmd_ready:表示硬件逻辑是否准备好接收指令。

function_id:指定自定义指令的功能ID,用于标识不同的自定义操作。

inputs_0 和 inputs_1:分别对应传递到自定义硬件逻辑的两个输入寄存器 rs1 和 rs2。

rsp_valid:指示自定义指令的处理结果是否有效。

rsp_ready:表示处理器是否准备好接收结果。

outputs_0:存储自定义指令的处理结果,通常会返回到处理器寄存器中。

用户自定义指令的时序图:

其中function_id是R指令的function7和function3,{ function7, function3}。

用户可以根据function_id和接收到的input0和input_1处理自己的逻辑,比如矩阵加速运算等。

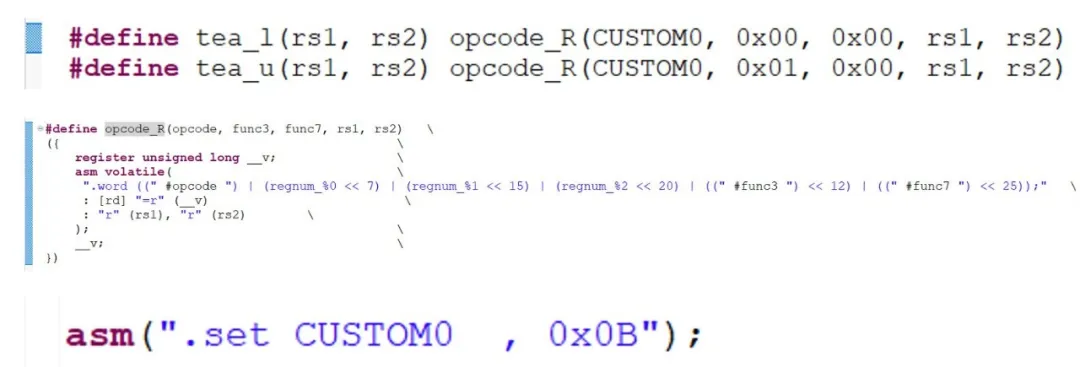

那么在RISC-V开发中如何撰写自己的代码呢?其实在生成RISCV的参考例子中,我们可以看到有一个用户自定义命令的demo(customInstructionDemo),在这个例子中我们可以看到如下的代码:

其中tea_l和tea_u传入rs1和rs2的寄存器的值,也就是对应时序图中的input_0和input_1,CUSTOM0保持不变,其实等于0x0B,而第二个和第三个参数对应的是function3和function7,对应的是时序图中的function_id信号,另外我们观察这个宏定义,有句话:[rd] "=r" (__v) , 表示将汇编语句的结果输出到一个名为__v的变量中,这个变量通过"=r"指定为一个通用寄存器(r)。rd是目标寄存器,通常是结果存储的地方。也就是接收将时序图中的outputs_0信号,然后返回给C语言程序处理。

Demo采用一个加密算法,分别通过RISC-V计算和FPGA测的逻辑计算进行对比,其结果表明拥有36倍的加速性能:

自定义指令可以显著提高特定算法的处理效率,尤其是在涉及到频繁运算或者特定硬件加速的任务中,比如数字信号处理(DSP)、图像处理或加密解密等。相信通过使用易灵思的Efinity软件,开发者可以配置和生成支持自定义指令的Sapphire SoC设计,进一步增强系统的功能与性能,加快您的设计。

随着易灵思提供的Efinity开发平台和RISC-V架构的强大支持,开发者能够在不依赖专有技术的前提下,根据具体应用需求快速实现硬件加速方案。这种高度可定制性使得RISC-V架构在面向未来的计算密集型应用中,具有巨大的潜力和竞争优势。通过自定义指令的灵活应用,开发者能够在实现高性能和低功耗的同时,进一步提升系统的整体效率和可靠性。

因此,无论是在高效的硬件加速应用中,还是在需要快速响应和高吞吐量的实时系统中,易灵思的RISC-V IP核与自定义指令的结合,提供了一个理想的解决方案,助力开发者在更短的时间内实现创新,推动技术的快速发展。

文章来源:易灵思