作者:Lucas,来源:易灵思官微

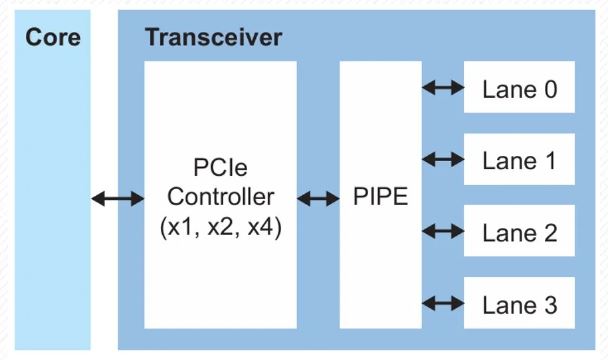

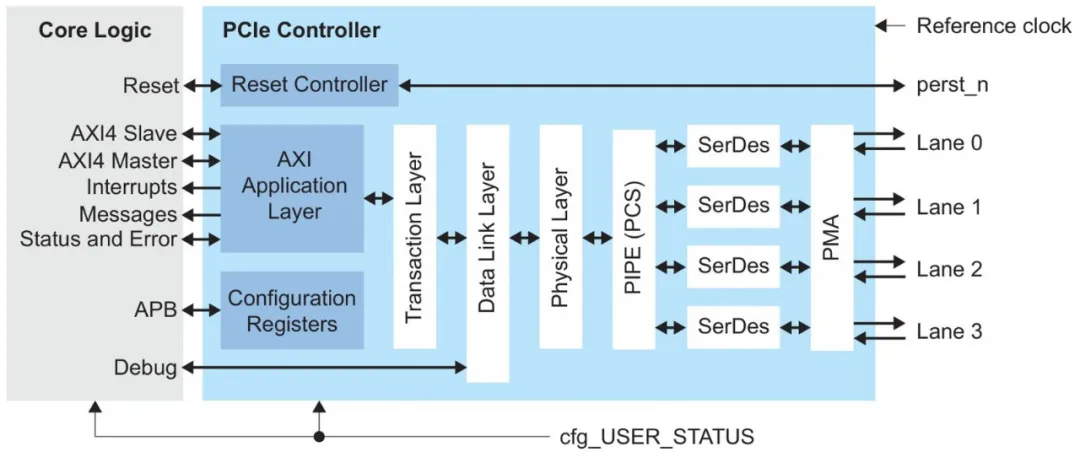

在数字经济飞速发展的今天,数据传输速率已成为硬件性能突破的核心瓶颈。作为国内首款适配中端FPGA的PCIe Gen4高速接口方案,钛金高速接口的闪亮登场,凭借高速低功耗特性、灵活配置能力与全面协议支持,成为FPGA硬件设备实现高速互联的首要选择。其控制器硬件架构由物理介质附加层(PMA)和物理编码子层(PCS)两大核心模块组成,其中PCS硬核支持SGMII、10GBase-R、PCIe Gen4及PMA Direct等多种协议。

简介

从性能参数来看,钛金PCIe控制器的硬实力尤为突出:其最高支持Gen4 x4的链路配置,单Lane速率可达16Gbps,整个链路的理论带宽最高可达64Gbps,相比友商的PCIe Gen3(单Lane 8Gbps)实现了速率翻倍,意味着数据传输效率直接翻倍提升;且单芯片可支持两个PCIe硬核控制器,能够轻松应对大型文件传输、高清视频流处理、算力密集型计算等高速数据交互场景。

在工作模式上,这款控制器提供了极强的灵活性,可根据实际应用需求配置为端点(EP)模式或根端口(RP)模式,适配不同的硬件拓扑架构。从数据流向来看,用户侧发起的PCIe操作会通过AXI4从端口驱动,而主机侧发起的操作则由AXI4主端口承载,这种双端口设计让控制器既能作为“数据接收端”响应外部请求,也能作为“数据发起端”主动发起交互,完美适配复杂系统中的数据交互需求。

无论是服务器、工业控制设备,还是高端显卡、存储阵列,钛金PCIe Gen4控制器都能凭借其低功耗、高速率、高兼容性的优势,成为连接硬件组件的“高速桥梁”。接下来,我们将深入解析其核心特性与技术细节,带大家全面认识这款PCIe硬核控制器。

核心特性

基于钛金PCIe控制器的硬件架构与协议支持,其核心特性围绕“高速、灵活、稳定、低耗”四大维度展开,既充分发挥了PCIe Gen4的协议优势,又针对实际应用场景进行了深度优化,具体特性如下:

2.1 极致速率与带宽,释放Gen4潜力

控制器最高支持PCIe Gen4 x4链路配置,单Lane传输速率稳定在16Gbps,链路总带宽可达64Gbps。这一性能指标意味着数据传输延迟大幅降低,单位时间内可传输的数据量翻倍,能够满足算力密集型场景(如AI推理、高性能计算)和大数据吞吐场景(如分布式存储、4K/8K视频编辑)的核心需求。相比友商产品,无需通过增加链路数量即可实现带宽翻倍提升,有效降低了硬件设计的复杂度与成本。在PCIe Gen4 x4硬核读写带宽测试中,写速度持续超过7500MB/s,读速度持续超过7400MB/s。

2.2 双模式配置 + AXI4-MM接口,适配多元场景

支持端点(EP)和根端口(RP)两种工作模式,可灵活融入不同的系统拓扑。EP模式下,控制器作为外设接口与主机互联(如显卡、网卡等外设场景);RP模式下,控制器可作为系统主控制器连接多个外设(如SSD、WiFi6等主控场景)。同时,通过AXI4-MM主/从端口实现数据交互,AXI4-MM协议作为业界主流的高性能总线协议,具备突发传输、乱序访问等优势,能够与FPGA逻辑架构高效协同,提升系统整体数据处理效率。

2.3 完整中断与消息机制,保障信号响应及时

配备专用中断接口和带内消息中断接口,全面支持传统中断、MSI和MSI-X三种中断模式。传统中断适用于简单场景的信号反馈,MSI通过将中断封装为消息包传输,减少了中断请求的资源占用,而MSI-X则支持更多独立中断向量,能为多设备、多任务场景提供精准的中断响应。三种模式的灵活适配,确保了从简单工业控制到复杂服务器系统等不同场景下,设备状态变化都能被及时捕获和处理。

2.4 虚拟化与多功能支持,应对复杂系统需求

支持SR-IOV(单根I/O虚拟化)技术,最多可配置4个物理函数(PF),每个物理函数又能支持多达16个虚拟函数(VF),总计支持64个虚拟函数。这一特性让单块PCIe设备能被多个虚拟机共享,无需为每个虚拟机配置独立硬件,大幅提升了服务器等虚拟化场景的硬件利用率。同时,多PF/VF的配置能力也让控制器能同时承载多个独立的业务负载,满足复杂系统的多功能集成需求。

2.5 高级错误报告与流量优化,提升系统可靠性

具备高级错误报告(AER)功能,能够实时监测传输过程中的各类错误并详细记录错误类型、位置等信息,方便工程师快速定位故障根源,降低系统维护成本。同时支持TLP处理提示(TPH)和路由标签(Steering Tag)技术,TPH能让主机提前知晓数据包的处理优先级,优化缓存利用效率;路由标签则可实现数据包的精准路由,避免传输拥堵,进一步提升了数据传输的流畅性和系统稳定性。

2.6 灵活复位与电源管理,平衡性能与功耗

支持功能级复位(FLR)和多种电源管理状态,FLR允许只复位单个PCIe功能而不影响整个链路或其他功能,特别适合多设备共享链路的场景(如服务器多网卡配置),避免了局部故障导致整体系统重启。电源管理方面则覆盖L0s、L1、L1子状态及L2等多种低功耗模式,可根据系统负载动态调整功耗,在保证高性能的同时降低待机或轻载状态下的能源消耗,适配移动设备、工业控制器等对功耗敏感的场景。在实际运行功耗测试中,功耗优于友商40%左右。

3.1物理层

物理层是PCIe数据传输的物理载体,完成PCS到PMA之间的数据交互,处理传输过程中的信号同步、失真校准等问题。钛金PCIe硬核控制器的物理层设计充分适配Gen4的高速特性,具体工作流程如下:

3.1.1接收(RX)侧工作流程

数据通过PIPE接口从PMA输入,每个Lane采用32位接口,时钟频率根据链路速率可配置为62MHz、125MHz、250MHz或500MHz(对应不同PCIe速率)。

数据首先被转换到核心时钟域,确保与控制器内部逻辑时钟同步。

每个Lane的数据独立进行解扰处理,恢复原始数据。

通过SKP序列(跳过序列)对多Lane数据进行去偏斜处理,确保所有Lane的数据包对齐,避免因传输延迟差异导致的数据错乱。

帧解码器解析对齐后的数据包,移除起始符(SOP)和结束符(EOP)等帧定界符,同时识别数据包类型并检测传输错误,最终将处理后的数据包发送至数据链路层。

3.1.2发送(TX)侧工作流程

从数据链路层接收128位宽的数据包及旁带信号。

帧编码器为数据包添加SOP和EOP定界符,确保接收端能正确识别数据包边界,并将数据包对齐到对应的传输Lane上。

数据包与链路训练状态机(LTSSM)生成的训练序列进行多路复用,链路训练阶段会屏蔽数据传输,由LTSSM控制各Lane进行协商;正常传输时则优先发送数据。

每个Lane的数据包独立进行扰码处理,然后通过PIPE接口输出到PMA。

3.1.3关键技术:SRIS与 RX Lane Margining

SRIS:支持独立参考时钟扩频(SRIS)技术,支持的频偏可达5600ppm。在SRIS模式下,控制器会按固定间隔发送SKP OS(跳过有序集),8b/10b编码模式下每128个符号发送一次,128b/130b编码模式下每32个块发送一次,用于补偿时钟偏差。若遇到大型TLP(事务层数据包)无法按时发送,会累积SKP OS并在TLP传输结束后集中发送,确保时钟同步不中断。

RX Lane Margining:接收端容限测试功能,允许系统软件在链路处于L0(正常工作)状态时,检测接收端在不同时序和电压条件下的传输余量。支持所有Lane同时进行容限测试,适配PIPE 4.4.1接口,通过可编程寄存器配置测试参数。该功能能提前发现接收端的稳定性隐患,帮助工程师优化硬件设计或调整传输参数,避免因电压波动、时序偏差导致的数据错误。

3.1.4链路训练与状态机(LTSSM)

物理层的核心控制逻辑是LTSSM,负责链路初始化、速率协商、状态监测等关键操作。上电或复位后,LTSSM会自动与对端设备进行协商,确定链路速率(如Gen4 16Gbps)、链路宽度(如x4)等参数,并通过训练序列校准信号时序,确保链路稳定后再进入数据传输状态。若传输过程中出现信号异常,LTSSM会自动触发链路恢复流程,若恢复失败则会通知上层进行错误处理,是保障物理层可靠性的“核心大脑”。

3.2 数据链路层

数据链路层位于物理层与事务层之间,核心职责是保障数据传输的完整性和有序性,相当于为数据传输添加了“安全防护网”,主要通过以下机制实现:

3.2.1接收(RX)侧工作流程

从物理层接收去除帧定界符后的数据包,首先通过CRC校验器验证数据包的LCRC(链路层CRC),检测数据在传输过程中是否因干扰发生错误。

若LCRC校验通过,剥离LCRC字段后将数据包转发至事务层;若校验失败,会根据错误类型触发重传请求或错误报告,确保错误数据不被上层处理。

独立的状态机负责数据链路层初始化,与对端设备协商流量控制、重传机制等参数,确保双方工作模式一致。

3.2.2发送(TX)侧工作流程

从事务层接收128位宽的数据包,为其添加LCRC字段(用于接收端校验),确保数据完整性可验证。

将数据链路层数据包(如ACK确认包、流量控制DLLP)与事务层TLP进行多路复用,按优先级调度传输顺序,确保确认包、流量控制包等关键信号优先传输,避免数据拥堵。

数据包存储在重放缓冲区中,若未收到对端的ACK确认,会自动重传该数据包,直到确认接收或触发超时错误,彻底解决数据丢失问题。

3.2.3核心机制:流量控制与重传保障

流量控制:采用基于信用的流量控制机制,对端设备会定期告知当前可用的接收缓冲区大小(信用值),本端控制器仅在信用值充足时发送数据包,避免因接收端缓冲区溢出导致数据丢失。

重传机制:重放缓冲区会暂存已发送但未确认的数据包,接收端通过ACK DLLP(数据链路层数据包)确认正确接收,若超时未收到确认或收到NACK(否定确认),则从缓冲区中取出数据包重新发送,确保数据传输的可靠性。

3.2.4数据链路层特性交换与流量控制扩展

数据链路特性交换:支持PCIe 4.0规范中的数据链路特性交换功能,通过配置寄存器启用后,控制器会在链路进入L0状态后发送特性DLLP,与对端协商流量控制等参数。若对端不支持该功能,控制器会在收到INITFC1 DLLP后切换至初始化状态,确保兼容性。

扩展流量控制:支持缩放流量控制,可通过寄存器修改缩放因子和信用限制。接收端会向对端通告头部和有效载荷的最大信用值,发送端根据信用值调整传输节奏,避免缓冲区溢出。若检测到流量控制协议违规(如超出信用额度限制),会触发FCPE(流量控制协议错误)并上报。

3.2.5 ACK聚合:提升传输效率

控制器支持ACK DLLP聚合功能,优化传输效率:正常情况下,每个接收的TLP对应一个ACK DLLP;若发送端正忙于传输TLP,ACK DLLP会等待当前TLP传输完成后发送。若等待期间收到新的TLP,控制器会将多ACK DLLP聚合为一个,携带最高序列号,减少DLLP的传输数量,节省链路带宽。

3.3 事务层

事务层是PCIe硬核的“上层大脑”,负责数据包的解析、路由、调度,以及与应用层(如AXI接口)的交互,核心是将应用层的请求转换为PCIe协议支持的TLP,同时将接收的TLP转换为应用层可识别的数据格式。

3.3.1接收(RX)侧工作流程

从数据链路层接收经过完整性校验的数据包,存入接收FIFO缓冲区,确保只有完整的数据包才会被处理,避免碎片化数据导致的解析错误。

对数据包进行解码,识别TLP的类型(如内存读写、I/O读写、配置读写、消息包等)、目标地址、数据长度等关键信息。

根据解码结果,将数据包转发至对应的主机接口(Posted包无需确认,如写操作;Non-Posted包需确认,如读操作)或完成包(Completion)接口,避免不同类型数据包的传输冲突。

对于中断消息等特殊数据包,直接转发至内部中断处理模块,确保及时响应。

3.3.2发送(TX)侧工作流程

从客户端逻辑(如AXI应用层)接收数据请求,按请求类型(Posted/Non-Posted/完成包)通过独立接口传入事务层。

状态机对请求进行处理,封装为符合PCIe协议的TLP,添加必要的头部信息(如地址、长度、类型标识)和ECRC(可选)。

按优先级对TLP进行调度,优先传输高优先级请求(如紧急消息、完成包),并通过公共数据路径转发至数据链路层,确保传输效率。

3.3.3核心价值:灵活适配与精准路由

事务层的设计核心是“适配性”和“高效性”:通过对不同类型请求的分类处理,适配内存访问、I/O控制、配置管理等多种应用场景;通过优先级调度和独立接口设计,避免传输拥堵;通过TLP头部的精准编码,实现数据包的定向路由,确保数据能准确送达目标设备或应用模块,是连接应用层与底层传输的“关键桥梁”。

3.4 AXI 应用层

AXI(Advanced eXtensible Interface)作为ARM推出的高性能总线协议,是钛金PCIe控制器连接用户逻辑(如FPGA内部模块、DMA引擎、内存控制器)的核心接口。简单来说,AXI应用层就像一位“翻译官”——将PCIe协议TLP(事务层数据包)转换为AXI信号,让用户逻辑无需理解复杂的PCIe协议就能直接交互;同时也能将用户逻辑的AXI请求转换为TLP,发送到PCIe链路上。

AXI 应用层包含三大核心接口,分工明确:

AXI 主接口(Master Interface):接收PCIe链路传来的请求(如主机对设备的读写),转换为AXI信号发送给用户逻辑(如设备的内存控制器),是“设备接收外部请求”的通道。

AXI 从接口(Slave Interface):接收用户逻辑发起的请求(如设备主动读取主机内存),转换为TLP发送到PCIe链路,是“设备主动发起请求”的通道。

消息与中断接口:处理PCIe链路上的消息包和中断信号,确保设备状态能及时反馈给主机。

3.4.1 AXI 主接口读操作:数据从PCIe到用户逻辑的“按需提取”

AXI主接口读操作负责将主机发起的“读请求TLP”转换为AXI信号,从用户逻辑中读取数据并返回给主机。读操作是“分裂事务”(地址和数据通道分离),就像先提交“取件单”(地址),再领取“包裹”(数据),流程清晰且高效。

1. 地址通道发起请求:控制器解析读请求TLP后,通过AXI主接口的地址通道向用户逻辑发送请求参数,包括TARGET_AXI_ARADDR(读起始地址)、TARGET_AXI_ARLEN(突发传输长度)、TARGET_AXI_ARSIZE(数据包大小)等,同时断言TARGET_AXI_ARVALID信号表示地址有效。

2. 用户逻辑确认地址:用户逻辑准备好后,断言TARGET_AXI_ARREADY信号,告知控制器“可开始读取数据”。

3. 数据通道返回数据:用户逻辑通过数据通道TARGET_AXI_RDATA发送数据,断言TARGET_AXI_RVALID表示数据有效,TARGET_AXI_RLAST标记最后一包数据。控制器通过TARGET_AXI_RREADY信号控制接收节奏,确保数据稳定接收。

4. 特殊场景处理:若TLP长度超过AXI最大突发长度,控制器会将其拆分为多个AXI读事务,用相同的TARGET_AXI_ARID标记,确保数据顺序正确;对于非对齐地址的TLP,控制器会自动调整读取范围,覆盖所需字节后过滤无效数据。

3.4.2 AXI 主接口写操作:数据从PCIe到用户逻辑的“精准投递”

AXI主接口写操作负责将PCIe链路上收到的“写请求TLP”转换为AXI信号,最终写入用户逻辑的内存或寄存器。与读操作的“地址先发、数据后到”不同,写操作的地址和数据通道是并行的,就像“快递单”和“包裹”同时发出,效率更高。

写操作的基本流程

地址通道启动:PCIe控制器收到主机发来的写请求TLP后,解析出目标地址、数据长度、突发传输参数等信息,通过AXI主接口的地址通道发送给用户逻辑。关键信号包括TARGET_AXI_AWADDR(写起始地址)、TARGET_AXI_AWLEN(突发传输长度)、TARGET_AXI_AWSIZE(单个数据包大小)、TARGET_AXI_AWVALID(地址有效信号)。

用户逻辑确认地址:用户逻辑(如内存控制器)收到地址后,通过TARGET_AXI_AWREADY信号确认“已收到地址,可以接收数据”。

数据通道传输:地址确认的同时,PCIe控制器通过数据通道发送实际数据,关键信号包括TARGET_AXI_WDATA(待写入的数据)、TARGET_AXI_WSTRB(字节掩码,标记有效字节)、TARGET_AXI_WLAST(最后一个数据标记)、TARGET_AXI_WVALID(数据有效信号)。

用户逻辑确认数据:用户逻辑接收数据后,通过TARGET_AXI_WREADY信号确认“数据已接收”。

写响应反馈:所有数据传输完成后,用户逻辑通过响应通道(TARGET_AXI_BRESP)反馈写操作结果(如“成功”“地址错误”),PCIe控制器再将结果封装为完成TLP,回传给主机。

关键特性与特殊场景

突发传输拆分:若PCIe TLP的长度超过AXI支持的最大突发长度,控制器会自动将TLP拆分为多个AXI突发传输,用相同的TARGET_AXI_AWID标记,保证用户逻辑能按顺序拼接。

错误标记转发:支持Poison Bit(错误标记位)转发,带错误标记的TLP会通过TARGET_AXI_AWUSER[43]位告知用户逻辑,非投递式(Non-Posted)写请求的错误响应会通过MASTER_AXI_BUSER信号标记,形成完整的错误溯源链。

严格排序:Posted写和Non-Posted写使用相同TARGET_AXI_AWID时,控制器会等待前一个Non-Posted写完成后再发送下一个,避免数据乱序。

零长度与非连续写入:忽略零长度写TLP(AXI不支持);非连续写入通过TARGET_AXI_WSTRB标记有效字节,用户逻辑仅写入指定字节。

3.4.3 AXI从接口读操作:主动拉取外部数据的“自主取件”

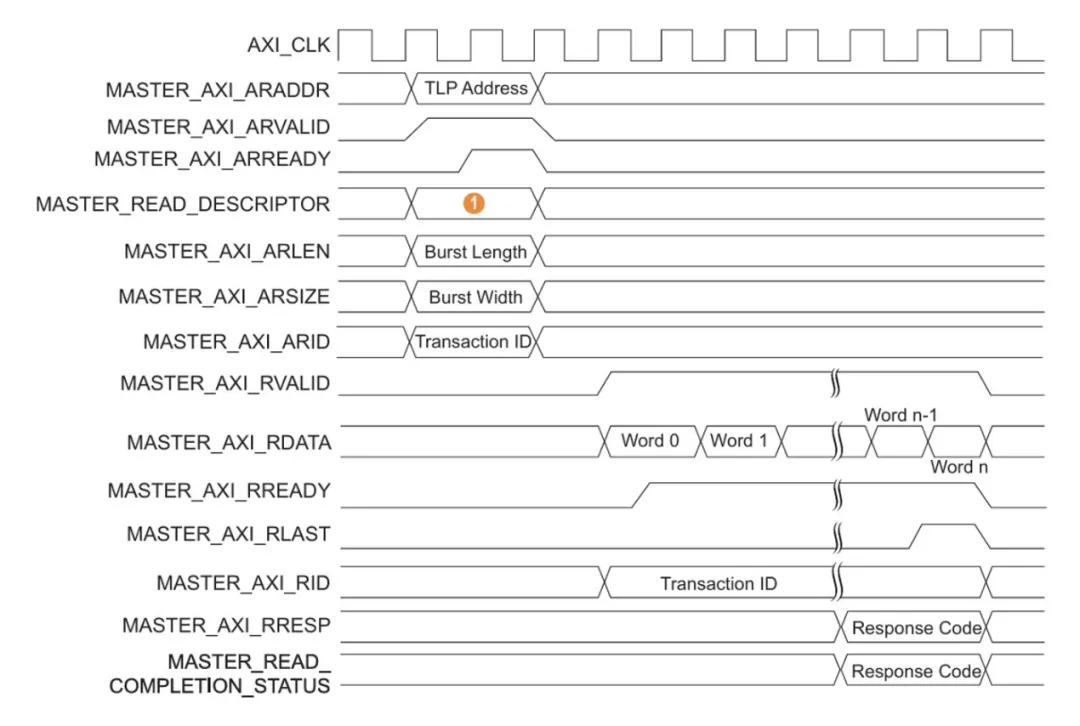

AXI从接口读操作负责将用户逻辑发起的“外部数据读取请求”转换为Non-Posted读TLP,发送至PCIe链路(如主机内存),并将获取到的数据返回给用户逻辑。读操作是设备“主动发起、按需获取”的过程,就像自主提交“取件申请”(地址请求),等待外部响应后领取“数据包裹”,流程独立且灵活。

操作的基本流程

地址通道发起请求:用户逻辑通过AXI从接口的读地址通道(MASTER_AXI_AR*)发送请求参数,包括目标地址、突发传输长度、数据包大小等,同时断言MASTER_AXI_ARVALID信号表示地址有效。控制器需满足两个条件才会接收请求:①链路信用充足(确保TLP可正常发送);②分裂完成表未存满,随后断言MASTER_AXI_ARREADY信号确认接收。

封装TLP并发送:控制器将用户逻辑的请求封装为符合PCIe协议的Non-Posted读TLP,同时在分裂完成表中记录请求状态(如请求标签、目标地址、数据长度等),避免请求丢失或乱序。

待外部数据响应:控制器持续监测PCIe链路,等待外部(如主机)返回的“完成TLP”(携带请求的数据),期间保持分裂完成表中的请求状态为“未完成”。

数据通道返回数据:收到完成TLP后,控制器解析数据并通过读数据通道(MASTER_AXI_R*)发送给用户逻辑:MASTER_AXI_RDATA携带有效数据,MASTER_AXI_RLAST标记最后一包数据,MASTER_AXI_RVALID表示数据有效。用户逻辑通过MASTER_AXI_RREADY信号控制接收节奏,确保数据稳定接收。

关键特性与特殊场景

请求权限限制:必须满足四大使用条件才能发起读请求:①仅根端口可发起I/O或配置读请求,端点无此权限;②端点发起内存读需确保“总线主控使能位”(PCI命令寄存器)已设置(通过FUNCTION_STATUS信号查询);③功能需处于D0 Active(正常工作)状态(通过FUNCTION_POWER_STATE信号确认);④功能未执行功能级复位(FLR),避免复位期间数据错乱。

地址与长度约束:请求长度受限于AXI_SLAVE_MAX_RD_TRANSFER_SIZE和MAX_READ_REQUEST_SIZE,若请求长度超过后者,控制器将直接拒绝处理。

分裂事务处理:若请求长度超过MAX_READ_REQUEST_SIZE且AXI_SLAVE_MAX_RD_TRANSFER_SIZE小于该值,控制器会按两者最小值拆分事务,所有拆分包使用相同请求标签,确保数据顺序正确。

3.4.4 AXI从接口写操作:主动推送数据的“主动投递”

AXI从接口写操作负责将用户逻辑生成的数据,通过主动发起写请求的方式发送至外部(如主机内存、其他外设),核心是“设备自主发起、数据主动推送”。与主接口写操作的“被动接收、并行传输”不同,从接口写操作是设备的“主动行为”,就像主动联系“收件人”(外部设备)并完成数据投递,分为Posted(投递式)和Non-Posted(非投递式)两种类型。

操作的基本流程

地址与数据并行发起:用户逻辑通过写地址通道(MASTER_AXI_AW*)发送目标地址、突发传输参数等信息,同时通过写数据通道(MASTER_AXI_W*)发送实际数据:关键信号包括MASTER_AXI_AWADDR(写起始地址)、MASTER_AXI_AWLEN(突发长度)、MASTER_AXI_WDATA(待写数据)、MASTER_AXI_WSTRB(字节掩码,标记有效字节)、MASTER_AXI_WLAST(最后一包标记),且同时断言MASTER_AXI_AWVALID和MASTER_AXI_WVALID信号表示地址与数据均有效。

控制器接收请求:控制器满足“链路信用充足+分裂完成表未满”条件后,分别断言MASTER_AXI_AWREADY(确认地址)和MASTER_AXI_WREADY(确认数据),接收地址参数与数据。

封装TLP并发送:控制器根据请求类型封装TLP:①Posted写(如内存写)直接生成TLP发送至PCIe链路,无需等待响应;②Non-Posted写(如I/O配置写)封装后发送,同时在分裂完成表中记录请求状态,等待外部完成响应。

写响应反馈(仅Non-Posted写):若为Non-Posted写,控制器收到外部返回的“完成TLP”(表示写操作结果)后,通过响应通道MASTER_AXI_BRESP向用户逻辑反馈结果(如“成功”“地址错误”),同时断言MASTER_AXI_BVALID信号表示响应有效。

关键特性与特殊场景

1. 请求类型差异处理:Posted写无需等待响应,传输效率更高(适用于大批量数据写入);Non-Posted写需等待响应,确保数据写入成功(适用于关键配置信息写入)。

2. 严格信号约束:字节使能(WSTRB)必须连续,不能出现离散有效位;突发传输过程中不能提前终止,需按预设长度完成数据发送,否则会导致协议违规。

3. 出站访问双模式:支持两种发起TLP的方式,适配不同场景:

静态方式(基于区域):通过APB接口预编程“区域寄存器”,每个区域对应一类TLP(如内存读、消息),包含固定头部信息。用户逻辑访问该区域AXI地址时,控制器自动生成TLP,适合固定类型的重复请求。

动态方式(边带描述符):用户逻辑直接通过边带信号提供完整TLP信息(如头部、数据长度),控制器直接封装发送,适合TLP信息频繁变化的场景,避免重复编程寄存器。

4. 长度限制与拆分:请求长度受限于AXI_SLAVE_MAX_WR_TRANSFER_SIZE,若该值大于MAX_PAYLOAD_SIZE且请求长度超界,控制器会按MAX_PAYLOAD_SIZE拆分事务,拆分包按顺序发送并共享同一请求标识。

3.4.5 入站消息接口:PCIe消息的“专用通道”

PCIe协议中,“消息”(Message)是一种特殊TLP,用于传递控制信号(如中断、电源管理指令)。钛金PCIe控制器设计了“入站消息接口”,专门处理从PCIe链路接收的消息,相当于为消息开辟了“专用高速通道”,避免与普通数据传输冲突。

核心信号与传输规则

信号组成:包括MSG_VALID(消息有效)、MSG_START/MSG_END(消息边界)、MSG_DATA(数据/头部标记)、MSG_BYTE_EN(字节使能)、MSG_VDH(厂商自定义头部标记),各信号协同指示消息的状态和类型。

传输规则:接口与AXI时钟同步,不支持背压,需用户外接FIFO(深度建议≥32)缓存消息;MSG_VALID为高时数据有效,传输头部时MSG_BYTE_EN为低,数据传输时字节使能连续。

中断消息的特殊处理

对于中断类消息,控制器会在消息输出的同时驱动对应的中断信号(INTA_OUT至INTD_OUT),避免无效状态切换;复位时所有中断信号自动撤销,确保初始状态一致。

3.4.6 入站PCIe到AXI地址转换

PCIe设备与AXI用户逻辑使用不同的地址空间,地址转换的作用是“翻译门牌号”,确保数据能准确映射。根端口(RP)与端点(EP)的转换规则略有不同:

根端口(RP)的地址转换

根端口有2个基地址寄存器(BAR0、BAR1),未匹配的地址默认使用BAR7。

转换后的AXI地址由两部分组成:高位来自地址转换寄存器(addr0和addr1),低位来自PCIe地址的低N位(N=addr0[5:0]+1)。

端点(EP)的地址转换

每个功能(PF/VF)有6个BAR,对应6组地址转换寄存器(每组含addr0和addr1)。

转换逻辑与根端口一致,AXI地址的低位长度由BAR的地址空间大小决定,确保只映射所需的地址空间。

3.4.7 AXI 主从接口的长度限制

PCIe和AXI协议对单次事务的长度(数据量)有明确限制,钛金控制器需遵循这些限制,避免协议违规导致的数据错误:

出站传输限制(AXI 到 PCIe)

读操作:受限于AXI_SLAVE_MAX_RD_TRANSFER_SIZE和MAX_READ_REQUEST_SIZE,若请求长度超过后者,控制器无法处理。

写操作:受限于AXI_SLAVE_MAX_WR_TRANSFER_SIZE,若该值大于MAX_PAYLOAD_SIZE且请求长度超界,控制器会按MAX_PAYLOAD_SIZE拆分事务。

入站传输限制(PCIe 到 AXI)

写操作:受限于MAX_PAYLOAD_SIZE,若AXI_MASTER_MAX_WR_TRANSFER_SIZE小于该值且TLP长度超界,按AXI_MASTER_MAX_WR_TRANSFER_SIZE拆分,所有拆分包使用相同AXI ID。

读操作:受限于MAX_READ_REQUEST_SIZE,若AXI_MASTER_MAX_RD_TRANSFER_SIZE小于该值且TLP长度超界,按两者最小值拆分,地址对齐到RCB(请求控制块)边界。

四、中断机制:设备与主机的“求救信号”

中断是设备向主机反馈状态的核心机制,相当于设备的“求救信号”-当设备发生特定事件(如数据接收完成、出现错误)时,通过中断通知主机及时处理。钛金PCIe控制器支持三种中断模式,适配不同复杂度的应用场景。

4.1 传统中断:简单场景的“基础信号”

传统中断(Legacy Interrupt)是PCI协议的经典中断模式,适配简单场景的信号反馈,核心特点是“引脚模拟”:

控制器模拟4个PCI中断引脚(INTA_IN、INTB_IN、INTC_IN、INTD_IN),多个功能可共享同一引脚,降低硬件资源占用。

端点侧通过这4个引脚向控制器发送中断信号:引脚从低变高时,控制器发送Assert_INTx消息;从高变低时,发送Deassert_INTx消息,告知主机中断的“断言”与“撤销”。

关键约束:使用传统中断时无法启用MSI/MSI-X;发送中断前需检查对应功能的“INTX禁用位”(通过FUNCTION_STATUS信号查询),禁用状态下不能发起中断;信号转换后需等待控制器的INT_ACK确认,才能发起下一次转换。

适用场景:简单工业控制设备、低复杂度外设,对中断响应速度和数量要求不高的场景。

4.2 MSI 中断:高效简洁的“消息型信号”

MSI(Message Signaled Interrupt)是PCIe协议引入的中断模式,核心是“用内存写TLP替代引脚信号”,大幅提升中断效率和灵活性:

核心原理

MSI将中断封装为“内存写TLP”,包含目标地址(主机内存的中断处理区域)和数据(中断标识信息)。设备发起中断时,无需操作引脚,直接向主机内存发送该TLP,主机通过监测内存写入事件识别中断。

关键特性

支持每个功能最多32个独立中断向量(数据模式),每个向量可对应不同的设备事件(如数据接收完成、发送超时、错误告警),实现“精准中断”。

中断地址和数据可通过配置寄存器灵活设置:主机通过配置写初始化MSI地址(高低32位)、数据、掩码寄存器,设备发起中断时读取这些参数生成TLP。

支持中断掩码与挂起:若中断向量被掩码(MSI_MASK位设置),设备会将中断挂起(置位MSI_PENDING_STATUS),待掩码清除后再发送中断TLP。

适用场景:中高复杂度设备,如网卡、存储控制器,需要多个中断向量且对响应速度有一定要求的场景。

工作流程

1. 主机初始化:通过配置写设置MSI地址、数据、掩码和使能位(MSI_ENABLE)。

2. 设备检查:通过MSI_ENABLE信号确认MSI已启用,监测中断事件或掩码清除事件。

3. 中断发送:若中断未被掩码,设备分配MSI区域,编程地址转换和描述符寄存器,生成出站写请求,数据为“向量号+MSI数据寄存器值”。

4. 挂起处理:若中断被掩码,置位对应挂起位,待掩码清除后重复步骤3。

4.3 MSI-X 中断:多向量场景的“终极方案”

MSI-X是MSI的增强版本,针对多任务、高复杂度设备设计,核心优势是“更多向量、更灵活配置”:

核心改进

支持每个功能最多2048个独立中断向量,远超MSI的32个,可满足多核心、多任务设备的精准中断需求(如高端FPGA、多端口网卡)。

每个向量可配置独立的地址和数据,无需共享地址空间,减少中断冲突。

引入“MSI-X表”和“挂起位阵列(PBA)”:MSI-X表存储每个向量的地址、数据和掩码状态,PBA存储每个向量的挂起状态,均存储在设备内存中,配置更灵活。

工作流程

1. 设备初始化:编程MSI-X表和PBA的内存地址(通过 MSI-X Table Offset Register和MSI-X Pending Interrupt Register )。

2. 主机配置:读取MSI-X表和PBA地址,初始化每个向量的地址、数据,并启用MSI-X(MSIX_ENABLE)。

3. 中断发送:设备监测到中断事件后,读取对应向量的表项,若未被掩码,分配MSI-X区域,生成出站写TLP发送;若被掩码,置位PBA中对应位。

4. 主机响应:主机接收TLP后,根据地址和数据识别向量,执行中断处理。

4.4 三种中断模式的对比与选型建议

选型核心原则:优先选择MSI-X(若设备支持),其次MSI,最后传统中断,平衡中断精准度和系统资源占用。

五、PCIe Gen4 核心技术参数对照表

综上所述,钛金PCIe Gen4高速接口方案作为国内首款适配中端FPGA的PCIe Gen4解决方案,凭借其卓越的高速低功耗特性、灵活的多协议支持以及创新的双控制器架构,为突破数据传输瓶颈提供了关键支撑。再次彰显了易灵思在FPGA领域深耕硬核技术、直击用户痛点的创新实力,持续为数字经济发展注入高速、灵活与高效的连接动力。