引言

工程师朋友们注意啦!今天要给大家安利一项FPGA领域的黑科技——西安智多晶微电子推出的LLCR(LVDS Local Clock Receiving)技术,使用本地PLL产生高速时钟,通过相位跟踪,对接收的LVDS信号进行实时跟踪,实现LVDS数据接收。

在PLL资源较少、多摄像头、多通道ADC及车载显示等需要高带宽、低资源的应用场景,LLCR技术通过单PLL动态相位跟踪,接收多路LVDS数据,省去随路时钟,最高节省50%以上时钟资源。

LLCR原理

LLCR是通过控制PLL进行动态相位调整实现对高速数据的跟踪,通过对接收数据P端和N端数据是否满足P=!N进行判决,对PLL进行增加或减少延迟操作,使PLL对应输出的时钟跟随接收数据,实现对LVDS数据的接收。

核心原理:

动态相位跟踪:通过PLL的动态相位调整功能,使本地产生的时钟能实时追踪输入LVDS数据的相位变化

智能边界锁定:利用LVDS差分信号的P=!N特性,自动寻找N端数据的右边界作为稳定采样点

资源优化:单PLL可接收多路非同源数据,相比传统方案节省50%时钟资源

技术亮点:

高带宽:最高可达900 Mbps稳定传输

多模式兼容:适配X1/X2/X4/X5及7:1等多种数据传输比率

强鲁棒性:支持链路中断后自动重新跟踪恢复

较少资源消耗:FPGA资源约50 LUT

LLCR关键技术实现

相位动态调整机制:

PLL动态相位调整,通过PHASE_SEL[1:0]、PHASEDIR、PHASESTEP控制信号实现:

相位选择:可动态切换PLL的CLKOP/CLKOS/CLKOS2/CLKOS3四路输出时钟

方向控制:PHASEDIR=0增加延迟,PHASEDIR=1减少延迟

步进调节:每个PHASESTEP脉冲实现VCO相位的1/(8*FVCO)微调

智能数据判决系统:

边界检测:通过xsIDDRSA模块将串行数据转化为并行数据后,实时检测P/N端信号关系

动态补偿:当P=!N时增加延迟,不满足时减少延迟,使时钟稳定在N端右边界

抗干扰设计:采用统计计数方式判定信号状态,避免瞬时干扰导致误判

典型应用场景

(1)LLCR跟踪一路数据

发送板卡发送LVDS 7:1数据,1路随路时钟和8路数据信号。接收端使用本地时钟产生高速时钟,通过LLCR IP跟踪数据,接收数据。

LVDS的随路时钟信号(黄色)和本地PLL产生信号(紫色),由于两个时钟不同源,两个时钟存在频偏和相位抖动等问题,随路信号(黄色)稳定时,本地PLL产生信号(紫色)随机抖动,两个信号无法同步,无法进行LVDS接收。

开启LLCR功能后,随路时钟信号(黄色)和LLCR控制PLL产生的本地信号(紫色)保持同步,解决两个时钟存在频偏和相位抖动等问题,可以完成LVDS接收。

(2)LLCR功能扩展

LLCR同时可以作为时钟控制模块配合LVDS接收模块一起使用,对接收的LVDS数据进行延迟调整。LLCR仅对随路时钟进行接收,根据随路时钟对本地产生的PLL输出高速时钟进行调整,将本地产生高速时钟连接LVDS 1:7模块,通过LVDS 1:7模块将串行高速数据转化为并行数据。在保留LLCR本地时钟跟随的功能下,可以对LVDS接收模块数据单独延迟,极大丰富了LLCR的功能。

(3)LLCR跟踪两路数据

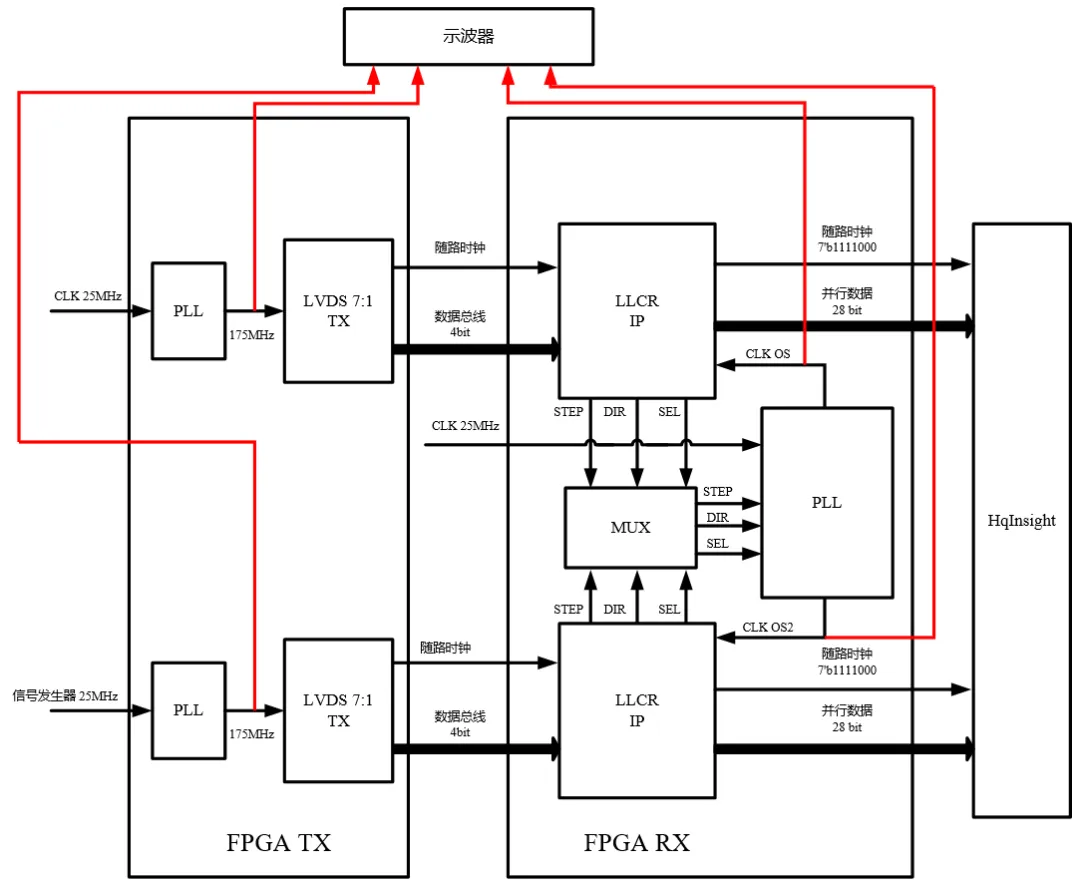

发送板卡发送LVDS 7:1数据,1路低速时钟和4路数据信号,和不同源的1路低速时钟和4路数据信号,共两组LVDS。

接收端均使用本地时钟上PLL产生CLKOS和CLKOS2两路高速时钟,使用两个LLCR分别跟踪两组数据,通过MUX模块将两组PLL控制信号组合。作用于PLL对输出的两路高速时钟相位进行调整,仅使用一个PLL接收两组不同源的LVDS数据,PLL资源减少50%。

结论

LLCR技术在FPGA的LVDS接收中减少PLL资源提供支持,本文基于西安智多晶微电子有限公司提供的《UG00079_LLCR_IP用户指南》文档编写,可在智多晶微电子有限公司官网进行查阅。希望本文能对您在FPGA设计和开发中有所帮助。对LLCR在FPGA中的使用有疑问,欢迎咨询西安智多晶微电子有限公司的技术支持团队!

文章来源:智多晶