作者:电子创新网编辑部

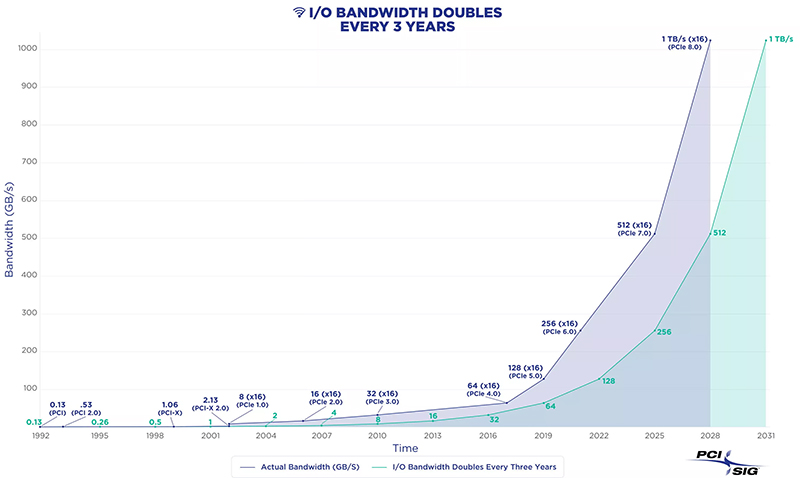

9 月 20 日,PCI 特别兴趣小组(PCI-SIG)正式公布 PCIe 8.0 的 0.3 草案规范。这意味着继 PCIe 7.0 完成之后,下一代高速互连标准的研发已全面提上日程。根据规划,PCIe 8.0 的最终规范预计将在 2028 年定稿,届时这项协议有望在 x16 通道双向连接下突破 1TB/s 的带宽大关。

这一进展不仅是标准演进的自然延续,更是高性能计算、AI、大模型训练以及超大规模数据中心对算力与互连提出新要求的直接体现。

1. 从 PCIe 1.0 到 8.0:20 年的“翻倍律”

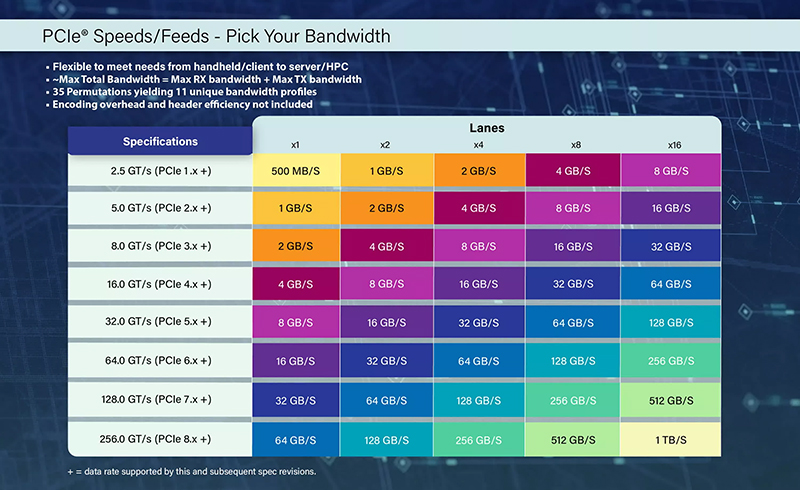

回顾 PCIe 的发展历程,从 1.0 到 7.0,几乎每一代都延续了带宽翻倍的节奏:

PCIe 3.0 / 4.0:8/16 GT/s,带宽 32GB/s ~ 64GB/s

PCIe 5.0:32 GT/s,最高 128GB/s,消费级 SSD 已突破 10GB/s 读速

PCIe 6.0:64 GT/s,256GB/s,美光扩展卡测试达 30GB/s

PCIe 7.0:128 GT/s,512GB/s,最终规范刚刚完成

PCIe 8.0(规划中):256 GT/s,1TB/s+

可以看到,每一次翻倍,都是整个产业技术进化的助推器。

2. 为什么是现在?AI 和数据中心的“带宽饥渴”

如果说 PCIe 5.0/6.0 还主要推动了消费级存储和显卡的升级,那么 PCIe 7.0/8.0 的意义,更多是面向 AI 训练集群、云计算和数据中心。

AI 大模型训练:GPU 集群需要更高 I/O 吞吐,避免“算力被喂不饱”。

数据中心:存储、网络与计算资源之间需要超高速通道,才能支撑 PB 级数据处理。

新兴算力需求:量子计算、边缘计算、军工与汽车电子等领域也需要低延迟、高可靠性的互连。

换句话说,PCIe 8.0 是算力基础设施升级的必然产物。

3. 技术挑战:突破 1TB/s 的背后

要实现 256 GT/s 的速率,PCI-SIG 面临多个技术挑战:

信号传输极限:可能需要探索 光学连接器 技术,以突破电学通道的瓶颈。

延迟与可靠性:在速率翻倍的同时,仍需保证稳定性。

功耗优化:AI 集群规模巨大,降低单通道功耗成为刚需。

向后兼容:继续支持 PCIe 既有生态,是标准成功的关键。

这些挑战决定了 PCIe 8.0 不只是“带宽的翻倍”,而是一次体系架构层面的演进。

4. 展望:2028 年的互连格局

按照 PCI-SIG 的路线图,PCIe 8.0 的 1.0 正式规范预计将在 2028 年完成。届时,AI 与数据中心或将成为 PCIe 8.0 的首发应用场景,随后才会逐渐渗透至消费级 PC。

可以预见,1TB/s 带宽的互连协议将成为 AI 算力军备竞赛的重要“底座”。谁能率先布局相关产品,谁就可能在新一轮的基础设施竞争中占据先机。

结论:PCIe 8.0 草案的发布不仅是一纸标准,更是全球算力产业即将进入“TB/s 互连时代”的信号。AI、数据中心、边缘计算与高性能计算企业,必须提前思考如何在未来几年内完成架构与产品的对接。

* 本文为原创文章,转载需注明作者、出处及原文链接,否则,本网站将保留追究其法律责任的权利。