自主可控再突破,智多晶 Seal 系列 FPGA 芯片通过权威认证!

judy 在 周二, 06/03/2025 - 10:26 提交

西安智多晶微电子有限公司自主研发的 Seal 5000、Sealion 2000 系列 FPGA/CPLD 芯片正式通过工业和信息化部电子第五研究所的评估认证

西安智多晶微电子有限公司自主研发的 Seal 5000、Sealion 2000 系列 FPGA/CPLD 芯片正式通过工业和信息化部电子第五研究所的评估认证

本文介绍了莱迪思FPGA如何赋能系统设计,特别是如何降低系统的BOM成本。通过集成莱迪思的FPGA解决方案,您可以构建一个经济高效的随机拣选系统。

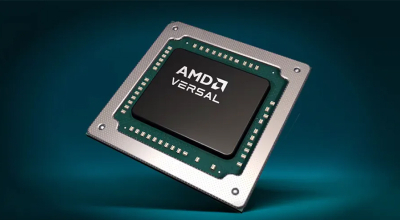

您是否准备将设计迁移到 AMD Versal™ 自适应 SoC?设计基线是一种行之有效的时序收敛方法,可在深入研究复杂的布局布线策略之前,帮您的 RTL 设计奠定坚实的基础

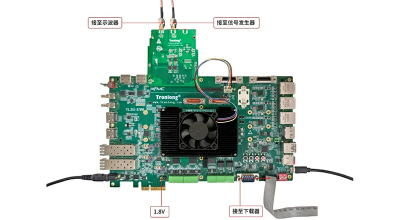

本文主要介绍基于Xilinx UltraScale+MPSoC XCZU7EV的高速AD采集与高速DA输出案例

随着生成式 AI 和大模型计算需求持续爆发,传统计算架构面临的挑战不断加剧。2024 年,全球训练一个百亿参数以上的大模型所需的计算资源年均增长超过 3 倍

各位朋友,大家好,熊猫君这次开个倒车,在这个广泛使用Xilinx(Altera)高端SoC的时代,分享一个“FPGA+ARM”实现的低功耗高性能传统方案。

AMD Versal™ AI Engine 是可编程的矢量处理器阵列,非常适合处理计算密集型 DSP 工作负载。

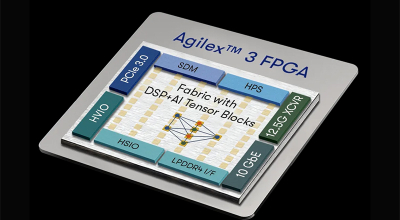

Agilex™ 3 器件家族可提供更高的性能、集成度和安全性,从而显著优化 FPGA 的功耗和成本。

AMD 自适应计算文档按一组标准设计进程进行组织,以便帮助您查找当前开发任务相关的内容。您可以在设计中心页面上访问 AMD Versal™ 自适应 SoC 设计进程。

XSBERT——专为FPGA高速收发器设计的调试利器,帮你一键生成误码率报告、实时扫描眼图,轻松验证链路稳定性!