YunSDR通信小课堂(第30讲)

judy 在 周一, 03/24/2025 - 14:17 提交

功能上,RF-DAC内的复混频器与RF-ADC内的混频器相同;不同之处在于它在RF-DAC中的作用是调制数据,而不是解调数据

功能上,RF-DAC内的复混频器与RF-ADC内的混频器相同;不同之处在于它在RF-DAC中的作用是调制数据,而不是解调数据

该系列教程由 AMD 的工业架构师 Tomas Thoresen 在 Hackster 上利用 FPGA 进行机器人应用的探索,下面先介绍一下这个项目

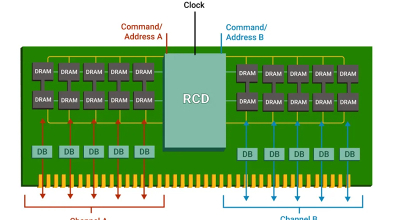

DDR5作为新一代内存接口标准,凭借4.8 GT/s至8.4 GT/s的超高速率、更高带宽和更低功耗

近日,美国半导体初创公司 Zero ASIC 宣布推出世界上第一款开放标准 eFPGA IP 产品Platypus。

Nexus 2平台的MIPI速度提升了3.2倍,配置时间快10倍,尺寸小5倍,单位逻辑DSP翻倍,INT8运算效率也更高

图像处理中最常用的技术之一是使用滑动窗口滤波器,该滤波器在图像上滑动一个 nxn 矩阵并对中心像素进行操作。

AMD Vivado™ Design Suite 实现突破性优化,可显著加快 Versal™ 自适应 SoC 硬件设计工作,与此同时大大简化了从旧架构到新架构的迁移

莱迪思和生态系统合作伙伴在此次展会上展示了基于莱迪思FPGA的最新重大创新成果,广泛应用于汽车、工业和安全网络边缘应用。

MAX◎ 10 FPGA 是一款单芯片通用解决方案。只需 3.3V电压,用户即可根据需求来设计芯片功能。即使在出货时尚未明确其应用场景,也无需担忧

在数字信号处理领域,FIR滤波器凭借其稳定性强、线性相位等优势,被广泛应用于各类信号处理场景。今天,就带大家深入解读西安智多晶微电子推出的FIR IP。