2025年嵌入式世界大会:莱迪思尖端FPGA解决方案

judy 在 周四, 03/20/2025 - 15:12 提交

莱迪思和生态系统合作伙伴在此次展会上展示了基于莱迪思FPGA的最新重大创新成果,广泛应用于汽车、工业和安全网络边缘应用。

莱迪思和生态系统合作伙伴在此次展会上展示了基于莱迪思FPGA的最新重大创新成果,广泛应用于汽车、工业和安全网络边缘应用。

MAX◎ 10 FPGA 是一款单芯片通用解决方案。只需 3.3V电压,用户即可根据需求来设计芯片功能。即使在出货时尚未明确其应用场景,也无需担忧

在数字信号处理领域,FIR滤波器凭借其稳定性强、线性相位等优势,被广泛应用于各类信号处理场景。今天,就带大家深入解读西安智多晶微电子推出的FIR IP。

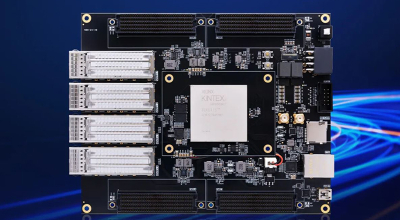

采用 AMD KINTEX UltraScale XCKU115 和 4 路 40G QSFP+ 光纤接口,整体带宽达 160Gbps,提供充足算力和超低延时支持

PCI-SIG 今天分享了 PCI Express 7.0 v0.9 规范,现在可供会员审查。

随着现代芯片的复杂性不断提高,验证成为芯片设计过程中最耗时和费力的部分,许多芯片设计项目通常要耗费大约60%-80%的项目资源用于验证

前面两篇文章详细介绍了DFT和FFT,今天介绍一下使用Verilog实现8点FFT。

安路科技与南京大学迎来关键合作进展——“南京大学-上海安路信息科技股份有限公司FPGA创新教育联合实验室”正式揭牌。

RF-DAC的数量、配置、结构和功能在不同的RFSoC设备和年代之间有所不同。图9.10突出显示了选定设备的RF-DAC在配置上的差异。

本文详细阐述 DSC IP 在 FPGA 中的应用特点,期望能为大家在选择 DSC 解决方案时提供有益参考。