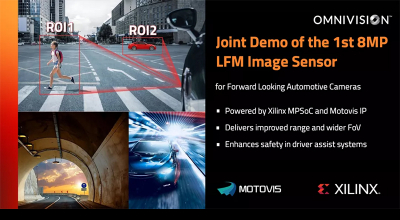

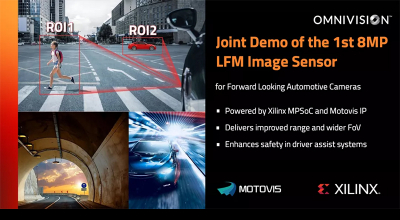

Motovis携手Xilinx和豪威集团在2022年CES上演示首款用于汽车前视摄像头系统的800万像素图像传感器系统

judy 在 周一, 01/17/2022 - 09:18 提交

由赛灵思 MPSoC 和 Motovis IP 协助打造的 OX08B40 提供更大的检测范围和更宽的视角,让汽车驾驶辅助系统更加安全

由赛灵思 MPSoC 和 Motovis IP 协助打造的 OX08B40 提供更大的检测范围和更宽的视角,让汽车驾驶辅助系统更加安全

关于傅立叶变换,无论是书本还是在网上可以很容易找到关于傅立叶变换的描述,但是大都是些故弄玄虚的文章,太过抽象,尽是一些让人看了就望而生畏的公式的罗列,让人很难能够从感性上得到理解

本文描述从 Spartan®-6 到 Spartan-7 FPGA 的迁移过程。

最近两年,Transformer在NLP、CV领域都取得了非常好的成绩。结合相关文章,Transformer的底层也是矩阵运算。使用FPGA加速,也会取得很好的效果。

VCK5000对于大多数开发者来说仍然是非常新的一款器件,由于VCK5000目前主要应用在数据中心进行AI推断方面的运算加速,所以开发者们对其性能和部署方式非常好奇

Xilinx的原语OSERDESE2是一种专用的并-串转换器,每个OSERDESE2模块都包括一个专用串行化程序用于数据和3状态控制。数据和3状态序列化程序都可以工作在SDR和DDR模式。

Vitis HLS 在从Vivaido HLS的升级换代中,以axi_master接口为起点的设计正在变得更易上手,其中很重要的一点就是更多的MAXI端口设计参数可以让用户通过指令传达到。这些参数可以分为两类

负责制定广为采用的PCI Express® (PCIe®)标准的组织PCI-SIG®今天宣布正式推出PCIe 6.0规范,传输速度达到64GT/s,是PCIe 5.0规格数据速率的两倍

在FPGA设计中,我们经常需要用寄存器来寄存某些“数量类”的变量,比如FIFO的深度啦、或者计数器的最大值啦;又或者输入输出信号也需要将位宽用parameter参数化以便更好的调用等。

一个完整的通信系统,是十分庞大的,没有几百上千人,在短时间内是做不好的。本文仅仅针对5G NR中的基带算法部分,做一个简单梳理。