Vitis软核固化代码流程

匿名 在 周四, 12/30/2021 - 10:00 提交

在搭建完Block Design以及硬件代码后,生成bit;bit文件生成成功后,点击Export Hardware,导出xsa文件:(xsa做连接使用)

在搭建完Block Design以及硬件代码后,生成bit;bit文件生成成功后,点击Export Hardware,导出xsa文件:(xsa做连接使用)

CCF体系结构专委会“开源定制计算”冬令营是主要面向研究生的免费公益活动。由CCF体系结构专委会主办,北京大学高能效计算与应用中心、赛灵思学术合作部联合承办。

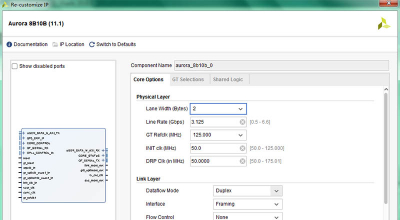

开门见山的说,跟DDR/PCIE/GTX这种复杂的IP相比,Aurora配置那是相当的简单。走着。

在Vitis HLS 工具中,要真正完成AXI总线突发,我们需要一个合适的代码风格并结合恰当的指令设置来达到这个目的。本章节带大家看看如何玩转AXI总线突发读写的代码风格-下。

基于ZYNQ的multiBoot测试

缺陷检测加速应用是一种机器视觉应用,可使用 Xilinx Vitis 视觉加速计算机视觉功能库自动检测缺陷、产品(例如水果、PCB)的成熟度以及在高速工厂管道中进行分类。

许多具有ASIC设计背景的Xllinx用户转向使用FPGA。这些工程师习惯于使用命令行模式下的工具流程,并希望在FPGA设计中继续使用类似的流程。

IDC中国发布了2021上半年人工智能市场份额报告,整体市场规模达21.8亿美元,相比去年同期增速42.2%。

Harris 工程师需要设计和验证一种跨多个 Xilinx® Virtex® FPGA 的信号处理系统。在这种人工密集型流程中,完成对子系统定点模型的仿真后

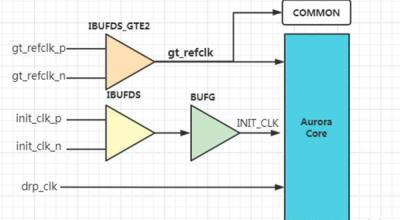

对于我们使用Xilinx或其他的成熟IP而言,IP相当于一个黑匣子,内部实现的逻辑功能我们知道,但是控制不了,只能默认OK;一般而言,成熟IP都是经过反复验证和使用,确实没有什么问题。所以,IP能不能用,首先要做的就是确保时钟和复位。