Xilinx FPGA平台GTX简易使用教程(二)GTX时钟篇

judy 在 周二, 01/04/2022 - 17:47 提交

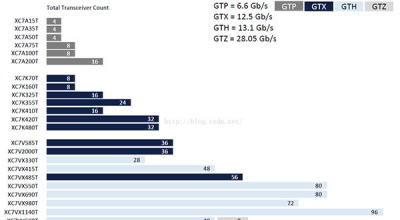

时钟就是脉搏,能否工作全靠它!话不多说,直接上干货!文中全部使用GTX代指GT Transceiver,同样适用于GTH。

时钟就是脉搏,能否工作全靠它!话不多说,直接上干货!文中全部使用GTX代指GT Transceiver,同样适用于GTH。

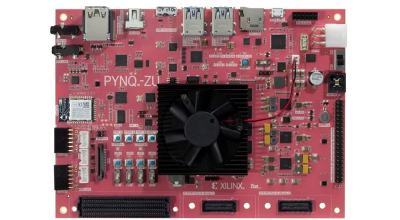

PYNQ-ZU是Zynq®UltraScale+™xczu5eg - 1sfvc784 MPSoc开发板,兼容Arduino、标准树莓派、LMC等各种接口,这使得PYNQ-ZU的具有极大的可拓展性与开源性。与PYNQ-Z2一样使用PYNQ框架,PYNQ 是 Xilinx 的一个开源项目

面积通常指一个设计消耗FPGA/CPLD的逻辑资源的数量,通常用可消耗的FF(触发器)和LUT(查找表)来衡量。速度指设计在芯片上稳定运行所能达到的最高频率,这个频率由设计的时序状况来决定,以及设计满足的时钟要求

本视频演示如何使用机器学习从单个高分辨率相机输入创建“虚拟”相机。 分析单个高分辨率 4K 摄像机输入以识别面部并自动跟踪、裁剪和创建多个高清 (HD) 虚拟流。

在Xilinx的DisplayPort 1.4 IP的文档中,提到支持的器件为Ultrascale/Ultrascale+/Versal系列,但很多的客户基于成本的考量希望能在7系列的器件中实现DP1.4。

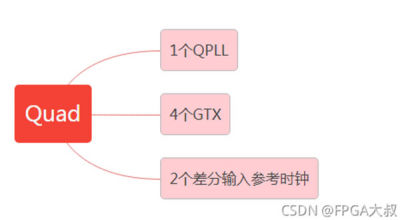

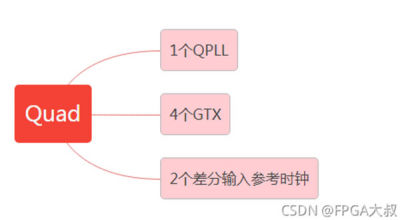

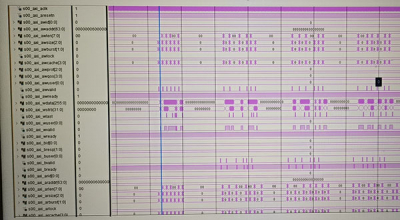

理解GTX的必备姿势,学起来!

FIFO最常被用来解决写、读不匹配的问题(时钟、位宽),总结下来,其实FIFO最大的作用就是缓冲。既然是缓冲,那么就要知道这个缓存的空间到底需要多大。

对于AXI4-FULL总线时,握手信号共有5路,包括写地址,写数据,写应答,读地址,读数据。当主机burst写时,每发起一次猝发交易,需要有一笔应答对应。

多看一些example design之后,你就会发现都是熟悉的配方~

可能很多FPGA初学者在刚开始学习FPGA设计的时候,经常听到类似于”这个信号需要打一拍、打两拍(寄存),以防止亚稳态问题的产生“这种话,但是对这个打拍和亚稳态问题还是一知半解,接下来结合一些资料谈下自己的理解。