Vitis AI RNN用户指南 (v1.4.1)

judy 在 周三, 12/22/2021 - 17:48 提交

本文提供了在Xilinx® 硬件平台上实现循环神经网络(RNN)的操作和参考信息。

本文提供了在Xilinx® 硬件平台上实现循环神经网络(RNN)的操作和参考信息。

libusb是一个免费的跨平台USB库,本文在windows平台下使用libusb库开发上位机程序与ZYNQ的USB接口进行数据收发测试。libusb可以支持WinUSB驱动,因此为ZYNQ的USB接口设备安装WinUSB驱动。

并非所有成像系统都需要昂贵。可以直接使用成本优化的 FPGA 和 CMOS 图像传感器来创建解决方案。

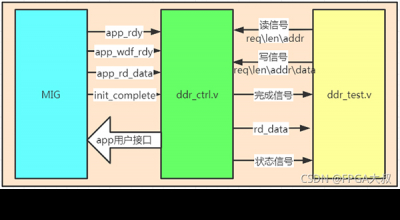

为了更方便的对DDR读写,我们对DDR再次封装成可复用的读写模块。

如何成长为一个合格的FPGA工程师?武林中,乾坤大挪移有七层的修炼境界,FPGA工程师技术修炼之路也是如此。

在实际应用中有很多FPGA板卡离工程师是有一定的距离,导致升级FPGA的mcs文件需要到现场,这样不方便也浪费时间。为此我们实现了基于通用网络传输方式来做远程升级的方案。

在这篇文章中,我们对Xilinx的XC2064进行了逆向工程,解释了它的内部电路以及 "比特流 "是如何对它进行编程的。

了解ddr的仿真模型建立

本方案利用 HLS 功能创建图像处理解决方案,在可编程逻辑中实现边缘检测 (Sobel)。

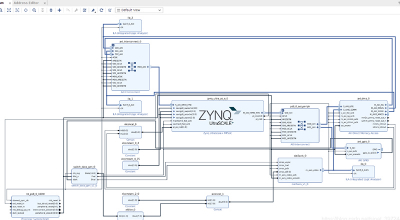

Petalinux 加速axi-dma内核驱动缓冲区读过程