【工程师分享】编译FFMpeg n4.2.5、OpenCV-3.4.16、OpenCV-4.5.4

judy 在 周一, 12/13/2021 - 09:55 提交

做测试时需要用OpenCV。虽然网络上有大量的关于编译OpenCV的教程,但是还是遇到了问题。因此记录了编译的过程,希望以后能更加顺利

做测试时需要用OpenCV。虽然网络上有大量的关于编译OpenCV的教程,但是还是遇到了问题。因此记录了编译的过程,希望以后能更加顺利

EGO1自从推出以来,为广大用户带来了丰富且易于上手的数字实验体验。今天我们为大家带了的是一款EGO1 AD/DA_AUDIO扩展卡的扩展解决方案。

前一代成功的无人机控制器基于Xilinx Zynq-7000打造,此次升级我们的工程团队采用了Xilinx Zynq Ultrascale+ MPSoC,其CPU实现了位置控制以及飞行轨迹跟踪。传感器和动作器通过FPGA逻辑连接

如何在 SDK 中查看 ELF 二进制文件的反汇编代码?本文介绍两种方法可以从 ELF 文件中获取反汇编代码。

LSTM是一种循环神经网络,它解决了以往RNN中存在的长期依赖问题(采用门控信号来避免梯度消失和爆炸,同时增强了对过去信息的记录能力),现在被广泛的应用于NLP领域。

两个AXIStream接口类型的IP核之间有时候需要加入一个Video(具有HS\VS)接口的IP核,这就需要将AXIStream类型的数据转换为Video类型,通过Video接口的IP核之后,又要将Video接口转换为AXIStream

如何从 SDK 中获取 ELF 文件的大小?本文分享两种方法。

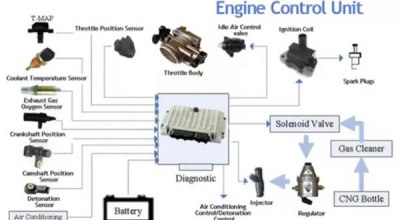

发动机管理几乎从未被认为是获得更好燃油经济性的一种方式。但在燃油价格不断上涨的今天,可以非常有效地使用电子技术来提高燃油经济性。

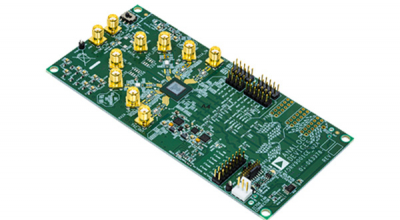

本文深入探讨了跳频(FH)的概念,以及如何通过灵活设计 ADRV9002 SDR 收发器的锁相环(PLL)架构来实现四大跳频特性。

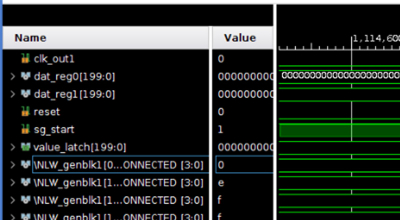

采用FPGA的CARRY4进位单元,每个CARRY4的COUT连接到下一个CARRY4的CIN,这样级联起来,形成延时链;每个COUT做为抽头输出到触发器,通过本地时钟进行数据采样