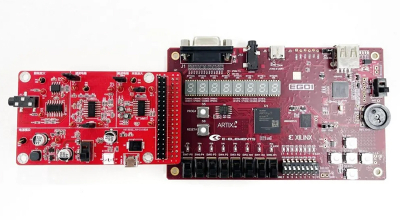

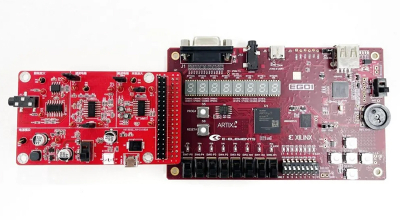

EGO1教育扩展模组系列-EGO1心电放大扩展卡

judy 在 周四, 12/02/2021 - 10:18 提交

EGO1自从推出以来,为广大用户带来了丰富且易于上手的数字实验体验。然而随着用户的不断需求升级,客户对于EGO1有了更高的需求。因此我们开发了更多的EGO1可扩增模组

EGO1自从推出以来,为广大用户带来了丰富且易于上手的数字实验体验。然而随着用户的不断需求升级,客户对于EGO1有了更高的需求。因此我们开发了更多的EGO1可扩增模组

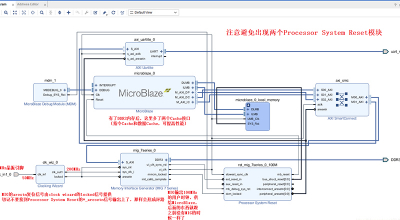

对于7系列FPGA,需要对GT的这两个时钟手工约束:对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

添加了DDR3内存以后,程序既可以运行在BRAM里面,也可以运行在DDR3内存里面。但如果运行在DDR3内存里面,固化起来会比较麻烦,需要借助SREC SPI Bootloader。

本篇博文是面向希望学习 Xilinx System Generator for DSP 入门知识的新手的系列博文第一讲。其中提供了有关执行下列操作的分步操作方法指南。

以CPU为中心的数据中心时代已经落下帷幕。业界已经证明,当今数据中心面临的挑战无法通过单一的工艺类型解决。在优化数据中心性能方面,FPGA、CPU和GPU都起着至关重要的作用

为期5周的Adapt-中国站作为Xilinx Adapt 2021的延伸,正持续在线上举行。最新回放集锦已新鲜出炉,干货满满,请速速查收!

本期主要介绍Vitis/ViTis AI的相关应用技巧和赛灵思应用商城的介绍,以及Versal AI引擎的资源和应用详解。

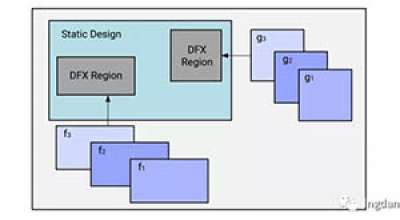

使用 DFX 有助于设计者转而采用更少或更小的器件,降低功耗并提高系统升级能力。随时按需加载功能,更有效利用芯片。

就在边缘设备上部署解决方案而言,硬件必须拥有充足的算力,才能处理ML算法工作负载。人们可以使用各种深度学习处理单元(DPU)配置对Kria K26 SOM进行配置,还能根据性能要求,将最适用的配置整合到设计内。

本白皮书描述了推荐的设计方法,以实现对 Xilinx® FPGA 器件资源的有效利用,并在 Vivado® 设计套件中更快地实现设计和时序收敛。提供了推荐方法背后的原因,以支持和实现明智的设计决策。