Xilinx FPGA平台DDR3设计保姆式教程(1)——DDR3基础简介

judy 在 周一, 12/06/2021 - 10:02 提交

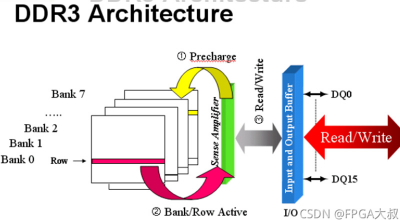

DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据的读取写入是按时钟同步的

DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据的读取写入是按时钟同步的

Xilinx FPGA MicroBlaze使用AXI 1G/2.5G Ethernet Subsystem(= Tri Mode Ethernet MAC + AXI Ethernet Buffer)以太网IP核驱动RTL8211FD千兆网口,并使用lwip2.1.2协议栈建立http服务器,支持IPv6

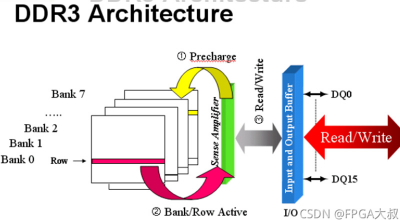

Kintex UltraScale FPGA KCU105 评估套件使用 MAX15301 及 MAX15303 PMBus 稳压器以及 MAX20751E 主控基于 Maxim PMBus 的电源系统。

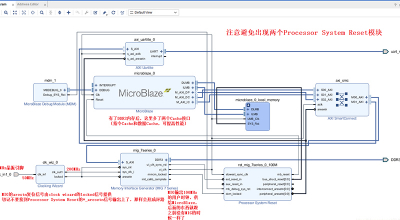

MicroBlaze™处理器参考指南提供了有关32位和64位软处理器MicroBlaze的信息,它是Vivado®设计套件的一部分。该文件旨在作为MicroBlaze硬件架构的指南。

在IBERT测试中需要注意的有以下两个要点

从官网能够很轻松的下载到vitis的安装包,可以下载Installer进行自动下载安装,也可以下载整个文件的压缩包,通过其中的setup进行安装。

Petalinux2020.01 内核DMA驱动调试过程分享

EGO1自从推出以来,为广大用户带来了丰富且易于上手的数字实验体验。然而随着用户的不断需求升级,客户对于EGO1有了更高的需求。因此我们开发了更多的EGO1可扩增模组

对于7系列FPGA,需要对GT的这两个时钟手工约束:对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

添加了DDR3内存以后,程序既可以运行在BRAM里面,也可以运行在DDR3内存里面。但如果运行在DDR3内存里面,固化起来会比较麻烦,需要借助SREC SPI Bootloader。