使用Jtag Master 调试FPGA程序

judy 在 周一, 11/29/2021 - 09:45 提交

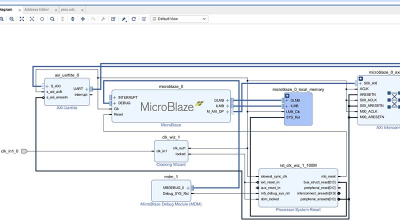

对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读写测试

对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读写测试

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。

本指南详细介绍Vivado®工具中Tcl脚本的使用,查询和修改内存设计的自定义流程。讨论了使用Tcl程序来定义和共享自定义命令。

在STA中,要分析上游器件和FPGA之间的时序关系就得指定input delay。

本文以浮点数Floating-point IP核将定点数转换为浮点数为例,详细讲解AXI DMA IP核的使用方法。

我在 Vivado 中有个 VHDL 项目。 UG900 用户指南指出: “后综合和后实现时序仿真仅就 Verilog 提供支持。不支持 VHDL 时序仿真。” 这是否意味着我不能在 VHDL 项目中运行时序仿真? 该项目有没有运行时序仿真的办法?

本篇简介教程演示了如何共享并访问位于远程实验室内的开发板或归其它同事所有的开发板。

这些实践旨在为用户提供快速入门指导,帮助其简要了解工具流程原理。我们选择了一项非常简单的设计,便于读者理解流程中的不同步骤。

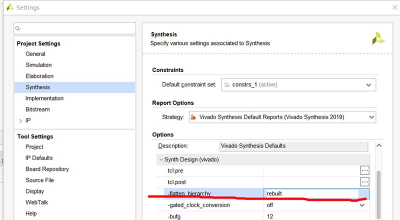

当选择为none,综合器优化的最少,当选择为full时,综合器优化的最多,选择rebuilt时,工具自动选择一个折中的方案,对当前工程做优化。如果在rebuilt的选项不希望一些信号被优化,则可以调用原语进行约束。

智能互联设备变得越来越普及,目前全球已经部署了数十亿台智能互联设备。这些智能设备存在于我们的手机、平板电脑、手表、家庭、汽车、城市和云端。在过去,智能设备是指有微控制器,运行某个软件的设备,如今的智能设备则需要执行类人任务。