Vivado快捷创建Vitis工程 (无需创建Platform Project)

guanxiao_505740 在 周一, 11/15/2021 - 14:50 提交

Vivado 2019.2开始就没有SDK了,需要在Vitis上创建应用工程。网上大部分都是创建Platform Project再创建Application Projet,然后在Application Projet里导入平台文件。其实一个简便的方法是直接创建Application Projett导入平台文件。

Vivado 2019.2开始就没有SDK了,需要在Vitis上创建应用工程。网上大部分都是创建Platform Project再创建Application Projet,然后在Application Projet里导入平台文件。其实一个简便的方法是直接创建Application Projett导入平台文件。

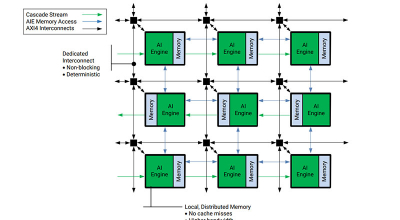

本文描述 AI 引擎内核编码的复杂性。

本次为期2天的线下讲座,将基于边缘端器件,搭配Xilinx MPSoC官方开发板ZCU104,引领开发者快速搭建Vitis AI开发环境,熟悉Vitis AI开发的设计流程及其基本技巧

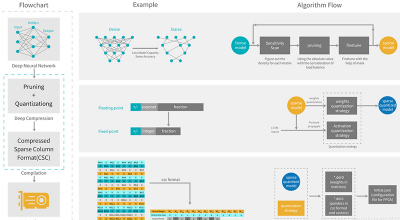

深鉴科技的DNNDK,是一个基于xilinx FPGA的SDK端的深度学习开发工具包,能够快速的实现深度学习的硬件化。本文来了解深鉴科技DNNDK内容。

了解 Vitis 2021.2 的新特性和增强功能

如果要在 UltraScale+ 器件中执行手动眼扫描,重新排列程序会导致 PCIe 重新训练,降至第一代产品的速度,并停留在那里。

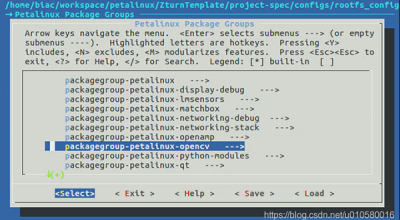

本文以Zturnboard为例介绍如何在SDSoC中使用OpenCV,本文在Ubuntu 16 64位,SDSoC2018.2(安装在ubuntu中)中测试通过。

Zynq 7020 的 PS 端(ARM 端)的外设 IO(也叫 IOP)分为 MIO 和 EMIO,他们有什么区别呢?

本指南总结了使用 Xilinx® Zynq® UltraScale+™ MPSoC 器件进行设计所需的以软件为中心的信息。

在这个项目中,我将创建一款用于智能办公室移动办公布局的应用。我将使用 Ultra96-V2 演示 Vitis AI 模型库和面向 PYNQ 的 DPU IP 核的编译流程。